千兆位無源光網絡

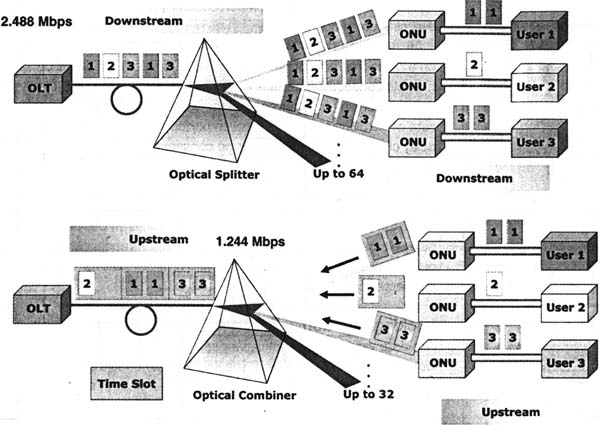

在2005年,FSAN(全業務接入網)組商定了千兆位無源光網絡(GPON)規范(見圖1)。此規范建立了語音、數據和視頻具有成本效益的遞交過程,這包括遞交到終端用戶的服務質量。‘first mile’接入技術采用光纖連接(光纖到用戶系統連接)可增加寬帶內容選擇。GPON很可能超過以太網無源光網絡成為未來光網絡的選擇。

GPON是一個點到多點系統,在此系統中,時分復用業務從光線路終端(OLT)經光纖送到光分路器,分路器重復分路業務到專門的相同數據流數。這些數據流的每一個直接到遠程光網絡單元(ONU),ONU提取指定所需的數據。在上游其過程與上述相反。

GPON在下游方向所提供的帶寬是上游方向的兩倍(64分路對32分路)。帶寬效率得到很大改善,因為定位的位較少,而更多位用于用戶。效率的改善是GPON技術的一個主要優點,這也為它正在成為數據遞交選擇技術的原因。

鎖定時間

GPON業務是異步的,下游規定為2.488Gbyte/s,上游定義為1.244Gbyte/s。在上游業務中,給每個用戶一個傳輸數據的時隙。從ONU到OLT的業務不是連續的,由數據突發組成。在上游方向的接收端,為了獲得高速數據需要系統同步和時鐘鎖定。

處理這些高速數據突發所需的鎖定時間,對于GPON是50位時間,而傳統系統允許相當長的鎖定時間(通常幾千位時間)。傳統技術(如時鐘數據恢復電路)不能用在這些情況下,所以,專門分立突發模式接收機用來滿足上游數據中固有的非常短鎖定時間的要求。然而,這類接收機消耗大量功率,導致占位面積不是最佳,使整個系統成本增加。

延遲和自適應

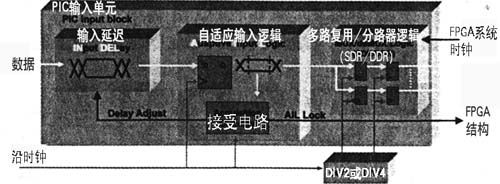

FPGA器件可解決此問題。輸入緩沖器包含適合不同線路條件的專門邏輯。每個可編程I/O單元包含4個可編程I/O(見圖2)。這些I/O的每個I/O都包含專門的邏輯,允許器件補償由每個引腳高達2Gbyte/s性能引起的定時變化。其關鍵是輸入延遲邏輯和自適應輸入邏輯(AIL)。

輸入延遲邏輯功能提供高達128個延遲單元,使輸入數據在0.45ps額定延遲。與輸入延遲邏輯相連的所有功能為監控和保持輸入時鐘/數據相位關系提供I/O邏輯性能,以保證單個I/O的建立和保持時間。檢測數據轉變點和延遲數據(為了使采樣時鐘沿不在轉變點處),從而正確地鎖定數據。此模式是一個自控制閉環系統,可由FPGA控制。它可跟蹤和補償由壓力、電壓和溫度引起的延遲變化,而這些變化可能導致參量超過整個系統控制范圍。

為了集中在無噪聲環境下,所有工作都是基于“伸縮窗:(‘sliding window’)原理。此窗取輸入數據的多個連續周期的抽點。為了在任何給定時間采樣,所有數據周期都呈現在延遲鏈上。例如,數據率為1.25Gbyte/s,則全部7個數據周期呈現在延遲鏈中。AIL寄存沿延遲線給定點(取決于窗位置)的9個連續數據位。一個中心分接頭寄存器(見圖3)做為數據有效窗的參考點,而周圍的寄存器確定窗寬度。根據來自延遲分接頭寄存器的反饋,定時通過延遲單元數(128)的數據輸入,選擇數據眼最好是無噪聲環境。

鎖定功能

數據有效窗大小做為最壞情況有效周期的函數是用戶可選擇的。窗大小應盡可能的大,而且最大總是小于最壞情況下有效數據周期。數據采集最壞情況起始位置是在數據轉變周期內對準AIL時。在窗內采樣到中心分接頭寄存器的左右寄存器的數據位,基于這些采樣,AIL開始以90ps步長進行搜索(圖4)。

所示的3個寄存器是:中心分接頭寄存器,取樣L寄存器和取樣R寄存器。在開始狀態取樣R寄存器是0、中心分接頭寄存器可以是1或0,取樣L寄存器是1。隨著AIL進行3步,當所有寄存器都示為1時,實現鎖定。這是在無噪聲環境和數據可靠情況下。

一旦搜索開始,AIL繼續單方向進行,因為這可防止噪聲環境下造成鎖定。當檢測到穩定數據,AIL繼續跟蹤由低速抖動/漂移、壓力、電壓和溫度變化引起的偏差,從而簡化數據恢復問題。

高性能器件

有些器件不僅僅包含工作在2Gbyte/s的高速并行I/O,而且也兼有FPGA結構和32個通道(工作在3.8Gbyte/s)。這與先進的嵌入式物理編碼子層相接合,為高速通信協議提供一個靈活的平臺方案。一些器件提供多結構ADIC單元,每個單元包含低功率高性能所需的50K ASIC型的門。

這些前置工作ASIC單元,使性能最大化地快速上市。它們包含GbE和10G Ethernet用的IP、SP14.2接口和存儲器控制器等。這些特性使這些器件的SC/M家庭適合集成GPON方案(如實發模式接收機功能),用一個FPGA做為復雜問題的單片系統方案。這比其他分立方案節省板面積50%~80%,節省功率4~8倍。

GPON參考設計可免費從Internet下載,參考設計為上游GPON業務終端展示可用的方案。此設計產生具有44位報頭和一個信頭(包含可編程定界符和長度半幀)的GPON幀。它可以仿真多ONU和在1幀內產生多分組突發。(彭京湘)

圖1 GPON功能框圖

圖2 FPGA輸入邏輯

圖3 伸縮數據有效窗

圖4 實現數據鎖定

【編輯推薦】