多核架構 高端網絡安全產品的必由之路

計算機網絡從20世紀60年代出現至今已經過了整整半個世紀,其使用目的從軍事、科研轉變為娛樂、商務,應用從簡單的郵件、BBS發展到搜索、即時消息、Web2.0、P2P、電子支付等等,參與網絡的終端與網民的數量快速增長,這些變化促使網絡信息高速公路不斷以增加帶寬容量來滿足發展的需要。特別是進入21世紀后,云計算、三網融合、移動互聯網、物聯網等新興技術再一次推動了網絡的飛速發展。根據中國互聯網信息中心(CNNIC)發布的***數據顯示,截止到2010年6月底我國網民已經達到4.2億,其中手機網民更超過了2.77億,中國互聯網國際出口帶寬達到了100萬Mbps。在如今的網絡建設中,10G的網絡數據流量已經屢見不鮮,而根據“吉爾德定律”,主干網帶寬還將繼續增加。

面對如此復雜的應用和龐大的用戶群體,如何解決高速網絡流量環境下的信息安全問題,特別是應用層安全,成為眾多信息安全企業亟待解決的問題。其實,自從信息安全產業誕生以來,對CPU高處理能力的需求就沒有停止過。為了獲得更高的處理性能,眾多企業也進行了很多嘗試。縱觀CPU技術的發展歷史可以簡單分為兩種方案:

◆提高單兵作戰的能力

在多核CPU出現之前,無論是不斷提高主頻,還是從X86到FPGA、ASIC、NP架構的轉變,其目的都是為了提高單顆CPU的處理能力。但由于散熱量高、開發難度大、開發周期長等諸多原因,上述技術的發展都不同程度受到了制約,難以滿足超高速流量下網絡安全產品對處理性能的需求。

◆發揮協同作戰的優勢

一個人的力量畢竟是有限的。由于散熱、時鐘頻率、制造工藝等原因,單顆CPU主頻的提升逐漸放緩(4GHz已經接近當前制造工藝的極限),而FPGA、AISC、NP等技術方案在需求變化快、要求應用層處理能力強的信息安全領域也顯得捉襟見肘。因此在尋求提高單顆CPU處理能力的同時,技術人員也一直沒有停止過對MP(Multi-Procesor)多處理器的研究。

SMP(Symmetric Multi-Processing)對稱處理結構是早期的一種方式,即在一塊主板上匯集一組處理器(多CPU),各CPU之間共享內存子系統以及總線結構,例如:我們常說的雙至強,也就是兩路CPU,是對稱處理器系統中最常見的一種。這種方式對主板和CPU的要求比較高,而且隨著CPU數目的增多,需要占用更大的主板面積、會帶來更大的功耗。

CMP(Chip Multiprocessors)即單芯片多處理器,也就是我們常說的多核。其核心思想是將大規模并行處理器中的SMP對稱多處理器集成到同一芯片內,各個處理器并行執行不同的進程。由于CMP結構被劃分成多個微處理器核來設計,每個核都比較簡單,有利于優化設計,解決了主頻提升帶來的高溫、高功耗的問題,但同時整個芯片提供了更高的處理性能,因此更有發展前途。

多核市場目前由兩大陣營組成:Intel和AMD公司組成的X86陣營;NetLogic、Cavium、Telira、ARM、IBM等公司組成的MIPS陣型。X86陣型采用CISC(Complex Instruction Set Computing)復雜指令集,按順序串行執行程序命令,控制簡單,更適合PC及中、低端服務器使用。而MIPS陣營采用的是RISC(Reduced Instruction Set Computing)精簡指令集,其相對于CISC指令來說格式統一,種類和尋找方式較少,并采用了“超標量和超流水線結構”,大大提高了處理速度,適用于網絡通信、信息安全、高端服務器等領域。

為了進一步提升在信息安全領域的競爭力,MIPS架構陣營在多核心的基礎上提出了一個新的概念SoC(System on Chip),即片上系統,將網絡連接、負責均衡、加/解密、應用加速等功能集成在一個芯片上。MIPS多核架構的發展為開發適應超高速網絡流量的網絡安全產品提供了基礎。

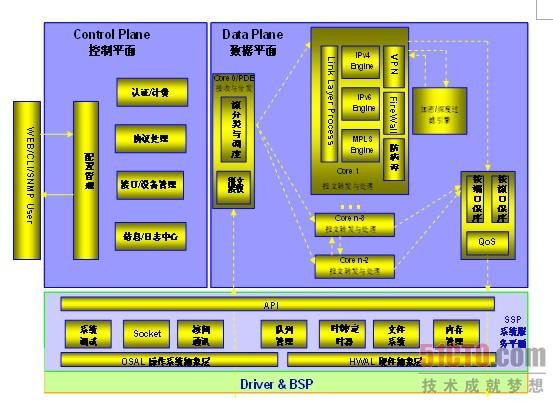

目前在多核CPU的使用上有兩種思路:一種是Linux系統的SMP;還有一種是NP的控制與數據分離的思路。SMP方式開發簡單、快捷,可以充分復用以前的軟件,但很難做到智能地調度各個CPU上的資源。而網絡安全產品對數據處理能力要求很高,不僅要求報文能夠得到及時處理,還要求能夠提供比較豐富的安全業務,如深度檢測、報文過濾等,所以有必要把數據處理和業務處理分離,由單獨的CPU并行處理,整個系統的性能將有很大的提升。聯想網御VSP平臺就是基于NP控制與數據分離的思想進行開發的。我們把軟件系統,抽象成四個子系統:控制平面、數據平面、系統服務平面、驅動與BSP。

圖1 VSP軟件平臺邏輯結構

為了充分調用多核心協同工作,聯想網御提出了Windrunner矩陣式并行處理算法,對多CPU內核進行矩陣式管理。例如:聯想網御的***端產品可以虛擬出多達64個vCPU:

圖2 Windrunner矩陣式并行處理算法示意圖

采用“8×8矩陣式并行處理系統”,將64顆vCPU排列為矩陣,從并行計算和流水線2個維度進行并行處理。所有的數據將被分配到8條流水線進行處理。每條流水線都具備8個環節,每個環節都有一個vCPU進行數據處理。“8×8矩陣式并行處理系統”不僅僅是多顆并行處理數據,還進一步引用流水線技術使得數據處理比原先更高效。Windrunner vCPU調度系統還會依據每條流水線上vCPU的工作飽和度情況實施調度,將較為空閑的vCPU調度到其他流水線中。

【編輯推薦】