操作系統(tǒng)之CPU知識(shí)掃盲

前言

CPU的英文全稱是(Central Processing Unit),中文意思翻譯中央處理器,是計(jì)算機(jī)的主要設(shè)備之一,功能主要是解釋計(jì)算機(jī)指令以及處理計(jì)算機(jī)軟件中的數(shù)據(jù)。計(jì)算機(jī)的可編程性主要是指對(duì)中央處理器的編程。

關(guān)于馮·諾依曼結(jié)構(gòu)

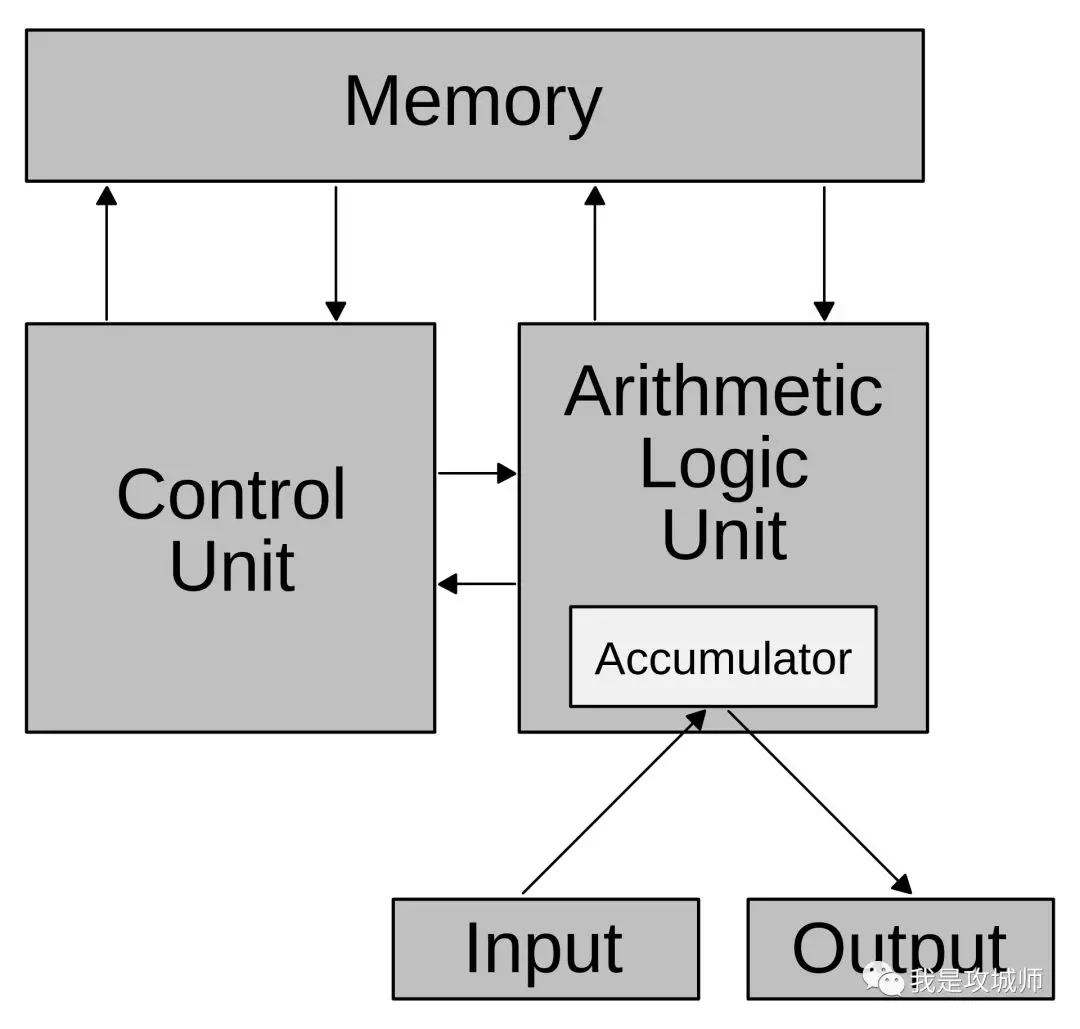

馮·諾依曼結(jié)構(gòu)(Von Neumann architecture)是一種將程序指令存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器合并在一起的計(jì)算機(jī)設(shè)計(jì)概念結(jié)構(gòu)。馮·諾依曼結(jié)構(gòu)隱約指導(dǎo)了將存儲(chǔ)設(shè)備與中央處理器分開ß的概念,因此依本結(jié)構(gòu)設(shè)計(jì)出的計(jì)算機(jī)又稱存儲(chǔ)程序計(jì)算機(jī),這也是目前大多數(shù)計(jì)算機(jī)設(shè)計(jì)的主要參考原則。

最早的計(jì)算機(jī)器僅內(nèi)含固定用途的程序。現(xiàn)代的某些計(jì)算機(jī)依然維持這樣的設(shè)計(jì)方式,通常是為了簡(jiǎn)化或教育目的。例如一個(gè)計(jì)算器僅有固定的數(shù)學(xué)計(jì)算程序,它不能拿來當(dāng)作文字處理軟件,更不能拿來玩游戲。若想要改變此機(jī)器的程序,你必須更改線路、更改結(jié)構(gòu)甚至重新設(shè)計(jì)此機(jī)器。當(dāng)然最早的計(jì)算機(jī)并沒有設(shè)計(jì)的那么可編程。當(dāng)時(shí)所謂的“重寫程序”很可能指的是紙筆設(shè)計(jì)程序步驟,接著制訂工程細(xì)節(jié),再施工將機(jī)器的電路配線或結(jié)構(gòu)改變。

而存儲(chǔ)程序型計(jì)算機(jī)的概念改變了這一切。借由創(chuàng)造一組指令集結(jié)構(gòu),并將所謂的運(yùn)算轉(zhuǎn)化成一串程序指令的運(yùn)行細(xì)節(jié),可讓程序運(yùn)行時(shí)自我修改程序的運(yùn)算內(nèi)容,讓此機(jī)器更有彈性。借著將指令當(dāng)成一種特別類型的靜態(tài)數(shù)據(jù),一臺(tái)存儲(chǔ)程序型計(jì)算機(jī)可輕易改變其程序,并在程控下改變其運(yùn)算內(nèi)容。 馮·諾伊曼結(jié)構(gòu)與存儲(chǔ)程序型計(jì)算機(jī)是互相通用的名詞。而哈佛結(jié)構(gòu)則是一種將程序數(shù)據(jù)與普通數(shù)據(jù)分開存儲(chǔ)的設(shè)計(jì)概念,但是它并未完全突破馮.諾伊曼架構(gòu)。

CPU執(zhí)行原理

CPU的主要運(yùn)作原理,不論其外觀,都是執(zhí)行儲(chǔ)存于被稱為程序里的一系列指令。在此討論的是遵循普遍的馮·諾伊曼結(jié)構(gòu)(von Neumann architecture)設(shè)計(jì)的裝置。程序以一系列數(shù)字儲(chǔ)存在計(jì)算機(jī)存儲(chǔ)器中。差不多所有的馮·諾伊曼CPU的運(yùn)作原理可分為四個(gè)階段:提取、解碼、執(zhí)行和寫回。

(1)提取

從程序內(nèi)存中檢索指令(為數(shù)值或一系列數(shù)值)。由程序計(jì)數(shù)器指定程序存儲(chǔ)器的位置,程序計(jì)數(shù)器保存供識(shí)別目前程序位置的數(shù)值。換言之,程序計(jì)數(shù)器記錄了CPU在目前程序里的蹤跡。提取指令之后,PC根據(jù)指令式長(zhǎng)度增加存儲(chǔ)器單元[iwordlength]。指令的提取常常必須從相對(duì)較慢的存儲(chǔ)器查找,導(dǎo)致CPU等候指令的送入。這個(gè)問題主要被論及在現(xiàn)代處理器的緩存和管線化架構(gòu)。

(2)解碼

CPU根據(jù)從存儲(chǔ)器提取到的指令來決定其執(zhí)行行為。在解碼階段,指令被拆解為有意義的片斷。根據(jù)CPU的指令集架構(gòu)(ISA)定義將數(shù)值解譯為指令[isa]。一部分的指令數(shù)值為運(yùn)算碼,其指示要進(jìn)行哪些運(yùn)算。其它的數(shù)值通常供給指令必要的信息

(3)執(zhí)行

在提取和解碼階段之后,接著進(jìn)入執(zhí)行階段。該階段中,連接到各種能夠進(jìn)行所需運(yùn)算的CPU部件。例如,要求一個(gè)加法運(yùn)算,算術(shù)邏輯單元將會(huì)連接到一組輸入和一組輸出。輸入提供了要相加的數(shù)值,而且在輸出將含有總和結(jié)果。ALU內(nèi)含電路系統(tǒng),以于輸出端完成簡(jiǎn)單的普通運(yùn)算和邏輯運(yùn)算(比如加法和比特運(yùn)算)。如果加法運(yùn)算產(chǎn)生一個(gè)對(duì)該CPU處理而言過大的結(jié)果,在標(biāo)志寄存器里,溢出標(biāo)志可能會(huì)被設(shè)置

(4)寫回

最終階段,寫回,以一定格式將執(zhí)行階段的結(jié)果簡(jiǎn)單的寫回。運(yùn)算結(jié)果經(jīng)常被寫進(jìn)CPU內(nèi)部的寄存器,以供隨后指令快速訪問。在其它案例中,運(yùn)算結(jié)果可能寫進(jìn)速度較慢,如容量較大且較便宜的主存

注意,這上面的4個(gè)階段與我們編寫程序是非常相關(guān)的,但編程語言里面可能會(huì)簡(jiǎn)化,并把2和3階段合并,分為:加載,處理,寫回。在多線程編程里面,了解這幾個(gè)概念至關(guān)重要,由此可以延伸,數(shù)據(jù)從哪里加載,在哪里執(zhí)行,***結(jié)果又寫回了哪里。指令數(shù)據(jù)一般從內(nèi)存里面加載,但是內(nèi)存的訪問時(shí)間,相比cpu慢了n多倍,所以為了加速處理,cpu一般把指令給加載到離cpu更近的寄存器里面,或者是L1,L2,L3的cache來提速,最終計(jì)算出來的結(jié)果,還要寫回內(nèi)存。正是因?yàn)閏pu執(zhí)行指令復(fù)雜,所以這里面其實(shí)牽扯到很多問題,比如多個(gè)線程如何協(xié)作處理任務(wù),以及如何保證程序數(shù)據(jù)的原子性,有序性,可見性。而這正是Java的內(nèi)存模型出現(xiàn)的意義。在其他不同的編程語言里面其實(shí)都有在操作系統(tǒng)之上抽象的內(nèi)存模型來應(yīng)對(duì)不同的cpu架構(gòu)的的差異,這一點(diǎn)需要注意。

多個(gè)單核CPU vs 單個(gè)多核CPU

多個(gè)單核CPU:

成本更高,因?yàn)槊總€(gè)CPU都需要一定的線路電路支持,這樣對(duì)主板上布局布線極為不便。并且當(dāng)運(yùn)行多線程任務(wù)時(shí),多線程間通信協(xié)同合作也是一個(gè)問題。依賴總線的傳輸,速度較慢,且每一個(gè)線程因?yàn)檫\(yùn)行在不同的CPU上。導(dǎo)致不同線程間各開一個(gè)Cache,會(huì)造成資源的浪費(fèi),同時(shí)如果線程間協(xié)作就會(huì)有冗余數(shù)據(jù)的產(chǎn)生,更加大了內(nèi)存的開銷。

單個(gè)多核CPU:

可以很好地規(guī)避基本上多個(gè)單核CPU提到的所有缺點(diǎn)。他不需要考慮硬件上的開銷以及復(fù)雜性問題,同時(shí)也可以很好地解決多線程間協(xié)同工作的問題,減少內(nèi)存的開銷,因?yàn)槎嗑€程程序在多核CPU中運(yùn)行是共用一塊內(nèi)存區(qū)的,數(shù)據(jù)的傳輸速度比總線來的要快同時(shí)不會(huì)有冗余數(shù)據(jù)的產(chǎn)生。單個(gè)多核CPU的問題也是顯而易見的,假設(shè)倆大程序,每一個(gè)程序都好多線程還幾乎用滿cache,它們分時(shí)使用CPU,那在程序間切換的時(shí)候,光指令和數(shù)據(jù)的替換就是個(gè)問題。

單個(gè)多核cpu已經(jīng)成為個(gè)人計(jì)算機(jī)的主流配置,多個(gè)多核的cpu在一些大型的服務(wù)器里面也很常見。

超線程

“超線程”(Hyperthreading Technology)技術(shù)就是通過采用特殊的硬件指令,可以把兩個(gè)邏輯內(nèi)核模擬成兩個(gè)物理超線程芯片,在單處理器中實(shí)現(xiàn)線程級(jí)的并行計(jì)算,同時(shí)在相應(yīng)的軟硬 件的支持下大幅度的提高運(yùn)行效能,從而使單處理器上模擬雙處理器的效能。其實(shí),從實(shí)質(zhì)上說,超線程是一種可以將CPU內(nèi)部暫時(shí)閑置處理資源充分“調(diào)動(dòng)”起來的技術(shù)。

每個(gè)單位時(shí)間內(nèi),CPU只能處理一個(gè)線程,以這樣的單位進(jìn)行,如果想要在單位時(shí)間內(nèi)處理超過一個(gè)的線程,是不可能的,除非是有兩個(gè)核心處理單元,英特爾的HT技術(shù)便是以單個(gè)核心處理單元,去整合兩個(gè)邏輯處理單元,也就是一個(gè)實(shí)體核心,兩個(gè)邏輯核心,在單位時(shí)間內(nèi)處理兩個(gè)線程,模擬雙核心運(yùn)作。

簡(jiǎn)單的說,超線程就是在單個(gè)core中,模擬出兩個(gè)邏輯處理單元,以此能夠提高程序執(zhí)行的并發(fā)能力,提高系統(tǒng)cpu資源的利用率。

至此,關(guān)于CPU的個(gè)數(shù),核數(shù),邏輯CPU的個(gè)數(shù)計(jì)算關(guān)系如下:

(1)總核數(shù) = 物理CPU個(gè)數(shù) X 每顆物理CPU的核數(shù)

(2)總邏輯CPU數(shù) = 物理CPU個(gè)數(shù) X 每顆物理CPU的核數(shù) X 超線程數(shù)

一些概念解釋如下:

- ① 物理CPU

- 實(shí)際Server中插槽上的CPU個(gè)數(shù)

- 物理cpu數(shù)量,可以數(shù)不重復(fù)的 physical id 有幾個(gè)

- ② 邏輯CPU

- Linux用戶對(duì) /proc/cpuinfo 這個(gè)文件肯定不陌生. 它是用來存儲(chǔ)cpu硬件信息的

- 信息內(nèi)容分別列出了processor 0 – n 的規(guī)格。這里需要注意,如果你認(rèn)為n就是真實(shí)的cpu數(shù)的話, 就大錯(cuò)特錯(cuò)了

- 一般情況,我們認(rèn)為一顆cpu可以有多核,加上intel的超線程技術(shù)(HT), 可以在邏輯上再分一倍數(shù)量的cpu core出來

- 邏輯CPU數(shù)量=物理cpu數(shù)量 x cpu cores 這個(gè)規(guī)格值 x 2(如果支持并開啟ht)

- 備注一下:Linux下top查看的CPU也是邏輯CPU個(gè)數(shù)

- ③ CPU核數(shù)

- 一塊CPU上面能處理數(shù)據(jù)的芯片組的數(shù)量、比如現(xiàn)在的i5 760,是雙核心四線程的CPU、而 i5 2250 是四核心四線程的CPU

- 一般來說,物理CPU個(gè)數(shù)×每顆核數(shù)就應(yīng)該等于邏輯CPU的個(gè)數(shù),如果不相等的話,則表示服務(wù)器的CPU支持超線程技術(shù)

(描述信息可滑動(dòng))

在linux上查看這些信息命令如下:

- # 查看物理CPU個(gè)數(shù)

- cat /proc/cpuinfo| grep "physical id"| sort| uniq| wc -l

- # 查看每個(gè)物理CPU中core的個(gè)數(shù)(即核數(shù))

- cat /proc/cpuinfo| grep "cpu cores"| uniq

- # 查看邏輯CPU的個(gè)數(shù)

- cat /proc/cpuinfo| grep "processor"| wc -l

舉例,在一個(gè)Mac Pro的機(jī)器上,可以通過關(guān)于本機(jī),系統(tǒng)報(bào)告選項(xiàng)中,看到當(dāng)前系統(tǒng)的基本配置情況,如下:

- 型號(hào)名稱:MacBook Pro

- 型號(hào)標(biāo)識(shí)符:MacBookPro11,4

- 處理器名稱:IntelCore i7

- 處理器速度:2.2GHz

- 處理器數(shù)目:1

- 核總數(shù):4

- L2 緩存(每個(gè)核):256KB

- L3 緩存:6MB

- 內(nèi)存:16GB

- Boot ROM 版本:187.0.0.0.0

- SMC 版本(系統(tǒng)):2.29f24

- 序列號(hào)(系統(tǒng)):C02SK27CG8WN

- 硬件 UUID:652D3965-1BF1-5614-AA0D-63DC5B6DD347

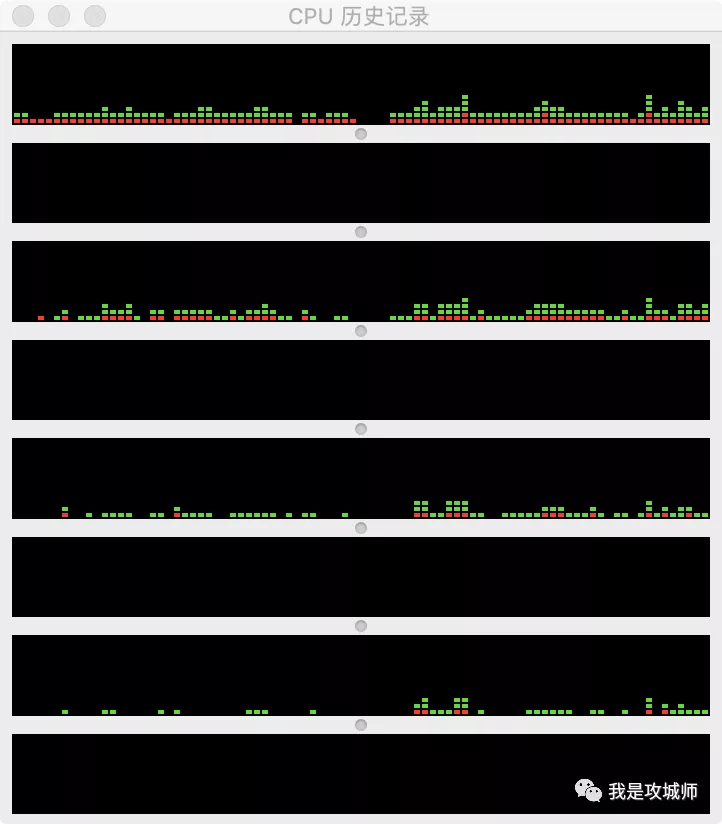

比如上面的信息中,顯示了當(dāng)前的系統(tǒng)物理上只擁有一個(gè)cpu,但是這個(gè)cpu有4個(gè)核。然后,我們查詢其邏輯cpu的個(gè)數(shù),會(huì)發(fā)現(xiàn)顯示是8個(gè):(在Mac上打開活動(dòng)監(jiān)視器,然后雙擊最下面的中間的cpu負(fù)載的地方,就可以看到)

這就是因?yàn)槊總€(gè)核又有2個(gè)超線程,所以8個(gè)邏輯cpu個(gè)數(shù)=1物理cpu個(gè)數(shù) * 4核 * 2個(gè)超線程,最終也就是說如果我要編寫一個(gè)多線程計(jì)算密集型的程序任務(wù),起的線程數(shù)可以以邏輯cpu的個(gè)數(shù)作為參照。當(dāng)然如果是io密集型的任務(wù),可以開的更多一點(diǎn)。

CPU性能參數(shù)

計(jì)算機(jī)的性能在很大程度上由CPU的性能決定,而CPU的性能主要體現(xiàn)在其運(yùn)行程序的速度上。影響運(yùn)行速度的性能指標(biāo)包括CPU的工作頻率、Cache容量、指令系統(tǒng)和邏輯結(jié)構(gòu)等參數(shù)。

大多數(shù)情況下,我們主要關(guān)注的是CPU的主頻,也稱時(shí)鐘頻率,是指同步電路中時(shí)鐘的基礎(chǔ)頻率,它以“每秒時(shí)鐘周期”(clock cycles per second)來度量,單位是兆赫(MHz)或千兆赫(GHz)用來表示CPU的運(yùn)算、處理數(shù)據(jù)的速度。通常,主頻越高,CPU處理數(shù)據(jù)的速度就越快。

在上面的mac的參數(shù)里面,我們能夠看到在Intel Core i7處理器下,主頻是2.2 GHz,當(dāng)前主頻高的處理器也在4 GHz之內(nèi),其主要原因主要在于散熱,提高主頻超過一定范圍后熱密度急速提高,很不經(jīng)濟(jì),也造成散熱困難。

總結(jié)

本文主要介紹了計(jì)算機(jī)操作系統(tǒng)中CPU有關(guān)的知識(shí),計(jì)算機(jī)的核心就在于CPU,了解CPU相關(guān)的知識(shí),可以讓我們更清楚我們的程序底層執(zhí)行的過程,從而寫出更健壯的代碼及調(diào)優(yōu)相關(guān)的程序。