鴻蒙內核源碼分析(寄存器篇) | ARM37個寄存器一網打盡, 不再神秘

本篇說清楚寄存器

ARM系列篇基于ARM720T.pdf文檔.

讀本篇之前建議先讀鴻蒙內核源碼分析(總目錄)arm體系系列篇.

寄存器的本質

寄存器從大一的計算機組成原理就開始聽到它,感覺很神秘,如夢如霧多年.揭開本質后才發現,寄存器就是一個32位的存儲空間,一個int變量而已,但它的厲害之處在于極高頻率的使用,讓人不敢相信是怎么做到的,不管再復雜再牛牛的應用程序,電商也好,游戲,直播也罷,到了它這里都變成了有限的十幾個寄存器在玩,簡直太神奇了. 本篇將清楚說明寄存器的數量和功能,至于它是如何把復雜的上層程序變成了這十幾個寄存器來玩?這是編譯器的事情,不在討論范圍之內.

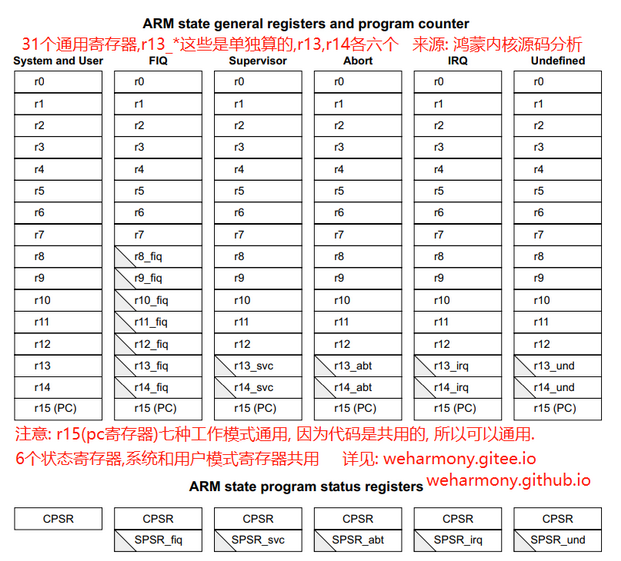

ARM7有37個寄存器,具體看圖說明:

這些寄存器不能同時顯示,處理器指令狀態和工作模式指定哪些寄存器可供使用,圖中一一對應.

● 其中31個通用32位寄存器,系統和用戶模式全程復用寄存器,而其余5中異常(或叫特權)模式從R8_* ~ R14_* 的寄存器叫模式專屬寄存器.

● 注意 r8 和 r8_fiq是兩個不同的寄存器,名字前綴是為了好記,管理方便,以示同級概念理解.如此湊成了31個寄存器.

● 其中r13寄存器用于SP寄存器,始終指向棧頂,因為每種工作模式都有獨立的運行棧,所以有獨立的寄存器去記住各自的棧頂.

● 同理r14寄存器用于LR寄存器,用于保存模式切換時的切換位置,也是獨立存在,說明模式間回跳時并不需要重新給r14_*賦值,只需在跳出去的時候保存即可.

● 系統和用戶模式共用r13(sp)和r14(lr)寄存器,所以在每個子函數的棧幀中都要保存上一個調用它函數的SP和LR值,自己執行完成后要從棧幀中恢復這兩個寄存器的值,否則無法界定回去后從哪里開始,從哪里計算偏移位置.

● r15(pc)寄存器是指向代碼段的,所有模式復用的原因是它是共用的,一份代碼,你運行與不允許,代碼段就在哪里,不增不減.

● 6個狀態寄存器,其中CPSR(1個)和SPSR_*(5個),它們主要用于自運行或發生模式切換后的各種狀態保存.

● CPSR:程序狀態寄存器(current program status register) (當前程序狀態寄存器),在任何處理器模式下被訪問。

● SPSR:程序狀態保存寄存器(saved program status register),每一種處理器模式下都有一個狀態寄存器SPSR,SPSR用于保存CPSR的狀態,以便異常返回后恢復異常發生時的工作狀態。當特定 的異常中斷發生時,這個寄存器用于存放當前程序狀態寄存器的內容。在異常中斷退出時,可以用SPSR來恢復CPSR。

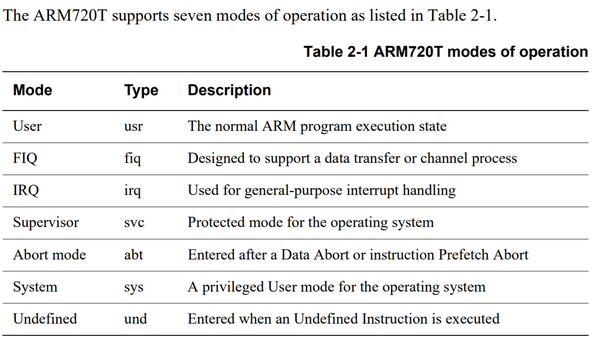

七種工作模式

關于工作模式在 鴻蒙內核源碼分析(總目錄)之工作模式篇中有詳細,可自行前往查看.此處只簡單說明下. 下圖來源于 ARM720T.pdf第43頁,在ARM體系中,CPU工作在以下七種模式中:

● 用戶模式(usr):屬于正常的用戶模式,不能直接切換到其他模式,ARM處理器正常的程序執行狀態。

● 快速中斷模式(fiq):支持高速數據傳輸及通道處理,FIQ異常響應時進入此模式

● 外部中斷模式(irq):用于通用中斷處理,IRQ異常響應時進入此模式

● 管理模式(svc):操作系統保護模式,系統復位和軟件中斷響應時進入此模式(由系統調用執行軟中斷SWI命令觸發)

● 數據訪問終止模式(abt):當數據或指令預取終止時進入該模式,可用于處理存儲器故障、實現虛擬存儲器和存儲器保護。

● 系統模式(sys):運行具有特權的操作系統任務,與用戶模式類似,但具有可以直接切換到其他模式等特權

● 未定義指令中止模式(und):處理未定義的指令陷阱,當未定義的指令執行時進入該模式,可用于支持硬件協處理器的軟件仿真。

除用戶模式外,其余6種工作模式都屬于特權模式

● 特權模式中除了系統模式以外的其余5種模式稱為異常模式

● 大多數程序運行于用戶模式

● 進入特權模式是為了處理中斷、異常、或者訪問被保護的系統資源

● 硬件權限級別:系統模式 > 異常模式 > 用戶模式

● 快中斷(fiq)與慢中斷(irq)區別:快中斷處理時禁止中斷

每種模式都有自己獨立的入口和獨立的運行棧空間. 系列篇之CPU篇 已介紹過只要提供了入口函數和運行空間,CPU就可以干活了.入口函數解決了指令來源問題,運行空間解決了指令的運行場地問題. 而且在多核情況下,每個CPU核的每種特權模式都有自己獨立的棧空間.注意是特權模式下的棧空間,用戶模式的棧空間是由用戶(應用)程序提供的.

R0 寄存器

R0是寄存器中的王牌,被稱為頭號寄存器,通用寄存器中它用的最高頻,隨便翻段匯編代碼都能看到它的影子.鴻蒙開機第一跳指令就是 r0 = 0

- reset_vector: //鴻蒙開機代碼

- /* clear register TPIDRPRW */

- mov r0, #0 @r0 = 0

- mcr p15, 0, r0, c13, c0, 4 @c0,c13 = 0, C13為進程標識符 含義見 ARM720T.PDF 第64頁

- /* do some early cpu setup: i/d cache disable, mmu disabled */ @禁用MMU, i/d緩存

- mrc p15, 0, r0, c1, c0, 0 @r0 = c1 ,c1寄存器詳細解釋見第64頁

- bic r0, #(1<<12) @位清除指令,清除r0的第11位

- bic r0, #(1<<2 | 1<<0) @清除第0和2位 ,禁止 MMU和緩存 0位:MMU enable/disable 2位:Cache enable/disable

- mcr p15, 0, r0, c1, c0, 0 @c1=r0

再看拿自旋鎖的匯編代碼,這些代碼都在系列篇中詳細講解過,可前往鴻蒙內核源碼分析(總目錄)自行查看.

- FUNCTION(ArchSpinLock) @非要拿到鎖

- mov r1, #1 @r1=1

- 1: @循環的作用,因SEV是廣播事件.不一定lock->rawLock的值已經改變了

- ldrex r2, [r0] @r0 = &lock->rawLock, 即 r2 = lock->rawLock

- cmp r2, #0 @r2和0比較

- wfene @不相等時,說明資源被占用,CPU核進入睡眠狀態

- strexeq r2, r1, [r0]@此時CPU被重新喚醒,嘗試令lock->rawLock=1,成功寫入則r2=0

- cmpeq r2, #0 @再來比較r2是否等于0,如果相等則獲取到了鎖

- bne 1b @如果不相等,繼續進入循環

- dmb @用DMB指令來隔離,以保證緩沖中的數據已經落實到RAM中

- bx lr @此時是一定拿到鎖了,跳回調用ArchSpinLock函數

R0被潛規則的干了兩件事,突出了它的重要性:

● 第一個參數 由R0保管,當然第二個參數就給R1保管

● 函數的返回值統一交給R0保管, 例如 a -> b ,b執行完會把返回值給r0,回到a后,a從r0取值,不管取到什么,它就認為這是b的返回值,默認都只認r0保存了返回值,這就是規定.

具體看一個C函數和它的匯編,在系列篇也已經講過,可自行翻看.

- //++++++++++++ square(c -> 匯編)++++++++++++++++++++++++

- int square(int a,int b){

- return a*b;

- }

- square(int, int):

- sub sp, sp, #8 @sp減去8,意思為給square分配棧空間,只用2個棧空間完成計算

- str r0, [sp, #4] @第一個參數入棧

- str r1, [sp] @第二個參數入棧

- ldr r1, [sp, #4] @取出第一個參數給r1

- ldr r2, [sp] @取出第二個參數給r2

- mul r0, r1, r2 @執行a*b給R0,返回值的工作一直是交給R0的

- add sp, sp, #8 @函數執行完了,要釋放申請的棧空間

- bx lr @子程序返回,等同于mov pc,lr,即跳到調用處

- //++++++++++++ fp(c -> 匯編)++++++++++++++++++++++++

- int fp(int b)

- {

- int a = 1;

- return square(a+b,a+b);

- }

- fp(int):

- push {r11, lr} @r11(fp)/lr入棧,保存調用者main的位置

- mov r11, sp @r11用于保存sp值,函數棧開始位置

- sub sp, sp, #8 @sp減去8,意思為給fp分配棧空間,只用2個棧空間完成計算

- str r0, [sp, #4] @先保存參數值,放在SP+4,此時r0中存放的是參數

- mov r0, #1 @r0=1

- str r0, [sp] @再把1也保存在SP的位置

- ldr r0, [sp] @把SP的值給R0

- ldr r1, [sp, #4] @把SP+4的值給R1

- add r1, r0, r1 @執行r1=a+b

- mov r0, r1 @r0=r1,用r0,r1傳參

- bl square(int, int)@先mov lr, pc 再mov pc square(int, int)

- mov sp, r11 @函數執行完了,要釋放申請的棧空間

- pop {r11, lr} @彈出r11和lr,lr是專用標簽,彈出就自動復制給lr寄存器

- bx lr @子程序返回,等同于mov pc,lr,即跳到調用處

這段代碼同樣適用于理解以下的各個寄存器.

R7 寄存器

為啥要單獨講R7寄存器,因為它偶爾作為特殊寄存器在使用.內核對上層應用提供了數百個系統調用功能,當發生系統調用時,在CPU工作模式切換過程中,系統調用號是一直保存在R7寄存器中的,通過系統調用號就能查詢到對應的注冊函數.具體在 系統調用篇中有詳細的過程說明,這里只列出部分代碼

- //4個參數的系統調用時底層處理

- static inline long __syscall4(long n, long a, long b, long c, long d)

- {

- register long a7 __asm__("a7") = n; //將系統調用號保存在R7寄存器

- register long a0 __asm__("a0") = a; //R0

- register long a1 __asm__("a1") = b; //R1

- register long a2 __asm__("a2") = c; //R2

- register long a3 __asm__("a3") = d; //R3

- __asm_syscall("r"(a7), "0"(a0), "r"(a1), "r"(a2), "r"(a3))

- }

- //切換到SVC模式后,由匯編代碼調用由C語言實現的系統調用統一入口

- LITE_OS_SEC_TEXT UINT32 *OsArmA32SyscallHandle(UINT32 *regs)

- {

- UINT32 ret;

- UINT8 nArgs;

- UINTPTR handle;

- UINT32 cmd = regs[REG_R7];// 從R7寄存器中取出系統調用號

- handle = g_syscallHandle[cmd];//查詢系統調用的注冊函數

- //...

- }

fp(R11) 寄存器

R11:可以用作通用寄存器,在開啟特定編譯選項時可以用作幀指針寄存器FP,用來實現棧回溯功能。 GNU編譯器(gcc)默認將R11作為存儲變量的通用寄存器,因而默認情況下無法使用FP的棧回溯功能。為支持調用棧解析功能,需要在編譯參數中添加-fno-omit-frame-pointer選項,提示編譯器將R11作為FP使用。

FP寄存器(Frame Point),幀指針寄存器,指向當前函數的父函數的棧幀起始地址。利用該寄存器可以得到父函數的棧幀,從棧幀中獲取父函數的FP,就可以得到祖父函數的棧幀,以此類推,可以追溯程序調用棧,得到函數間的調用關系。

在鴻蒙內核R11是當FP寄存器使用.

SP(R13) 寄存器

SP:棧指針寄存器(stack pointer),指向函數棧的棧頂,如此 fp 和 sp 就劃定了函數棧的范圍,函數在運行期間除了動態申請的內存要跑出去玩,其余就在這塊空間里玩.

在鴻蒙內核R13是當SP寄存器使用.

LR(R14) 寄存器

異常的發生會導致程序正常運行的被打斷, 并將控制流轉移到相應的異常處理(異常響應),有些異常(fiq、irq)事件處理后,系統還希望能回 到當初異常發生時被打斷的源程序斷點處繼續完成源程序的執行(異常返回),這就需要一種解決方案, 用于記錄源程序的斷點位置,以便正確的異常返回。 類似的還有子程序的調用和 返回。在主程序中(通過子程序調用指令)調用子程序時,也需要記錄下主程序中的調用點位置,以便將來的子程序的返回。 LR:鏈接寄存器(linked pointer),就是用來解決上述問題的,ARM處理器中使用 R14實現對斷點和調用點的記錄,即R14用作返回連接寄存器(LR),確保回來知道自己從哪個位置中斷,以便繼續執行.

在鴻蒙內核R14是當LR寄存器使用.

PC(R15) 寄存器

pc:程序計數寄存器(Program Counter Register) 向代碼段取指令,指向代碼段具體位置,PC寄存器涉及到arm的流水線結構設計,具體在后續流水線篇中詳細說明,敬請關注. 在鴻蒙內核R15是當PC寄存器使用.

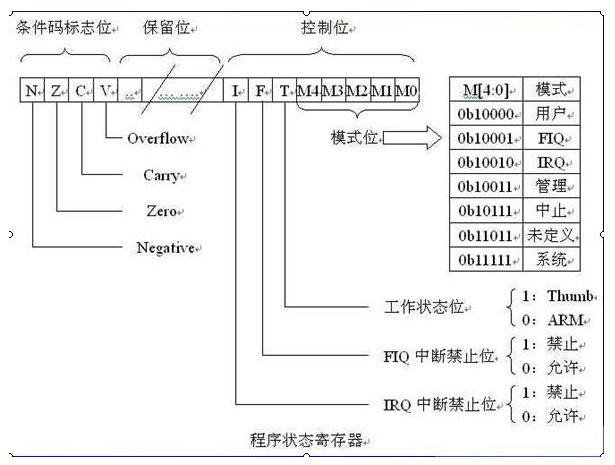

CPSR 寄存器

CPSR(current program status register)當前程序的狀態寄存器 CPSR有4個8位區域:標志域(F)、狀態域(S)、擴展域(X)、控制域(C) 32 位的程序狀態寄存器可分為4 個域:

1.位[31:24]為條件標志位域,用f 表示;

2.位[23:16]為狀態位域,用s 表示;

3.位[15:8]為擴展位域,用x 表示;

4.位[7:0]為控制位域,用c 表示;

CPSR和其他寄存器不一樣,其他寄存器是用來存放數據的,都是整個寄存器具有一個含義. 而CPSR寄存器是按位起作用的,也就是說,它的每一位都有專門的含義,記錄特定的信息.

CPSR的低8位(包括I、F、T和M[4:0])稱為控制位,程序無法修改, 除非CPU運行于特權模式下,程序才能修改控制位

N、Z、C、V均為條件碼標志位。它們的內容可被算術或邏輯運算的結果所改變, 并且可以決定某條指令是否被執行!意義重大!

● CPSR的第31位是 N,符號標志位。它記錄相關指令執行后,其結果是否為負. 如果為負 N = 1,如果是非負數 N = 0.

● CPSR的第30位是Z,0標志位。它記錄相關指令執行后,其結果是否為0. 如果結果為0.那么Z = 1.如果結果不為0,那么Z = 0.

● CPSR的第29位是C,進位標志位(Carry)。一般情況下,進行無符號數的運算。 加法運算:當運算結果產生了進位時(無符號數溢出),C=1,否則C=0。 減法運算(包括CMP):當運算時產生了借位時(無符號數溢出),C=0,否則C=1。

● CPSR的第28位是V,溢出標志位(Overflow)。在進行有符號數運算的時候, 如果超過了機器所能標識的范圍,稱為溢出。

MSR{條件} 程序狀態寄存器(CPSR 或SPSR)_<域>,操作數 MSR 指令用于將操作數的內容傳送到程序狀態寄存器的特定域中 示例如下:

- MSR CPSR,R0 @傳送R0 的內容到CPSR

- MSR SPSR,R0 @傳送R0 的內容到SPSR

- MSR CPSR_c,R0 @傳送R0 的內容到CPSR,但僅僅修改CPSR中的控制位域

MRS{條件} 通用寄存器,程序狀態寄存器(CPSR 或SPSR) MRS 指令用于將程序狀態寄存器的內容傳送到通用寄存器中。該指令一般用在以下兩種情況: 1) 當需要改變程序狀態寄存器的內容時,可用MRS 將程序狀態寄存器的內容讀入通用寄存器,修改后再寫回程序狀態寄存器。 2) 當在異常處理或進程切換時,需要保存程序狀態寄存器的值,可先用該指令讀出程序狀態寄存器的值,然后保存。 示例如下:

- MRS R0,CPSR @傳送CPSR 的內容到R0

- MRS R0,SPSR @傳送SPSR 的內容到R0

- @MRS指令是唯一可以直接讀取CPSR和SPSR寄存器的指令

SPSR 寄存器

SPSR(saved program status register)程序狀態保存寄存器.五種異常模式下一個狀態寄存器SPSR,用于保存CPSR的狀態,以便異常返回后恢復異常發生時的工作狀態。

● 1、SPSR 為 CPSR 中斷時刻的副本,退出中斷后,將SPSR中數據恢復到CPSR中。

● 2、用戶模式和系統模式下SPSR不可用,所以SPSR寄存器只有5個

留個問題

從R11 ~ R15 寄存器除了R12都用著專用寄存器,用作為特殊用途,單獨獨R12夾在中間不上不下的,這又是為什么呢?

參與貢獻

● 訪問注解倉庫地址

● Fork 本倉庫 >> 新建 Feat_xxx 分支 >> 提交代碼注解 >> 新建 Pull Request

● 新建 Issue