讓芯片設計更加敏捷的兩個關鍵方法

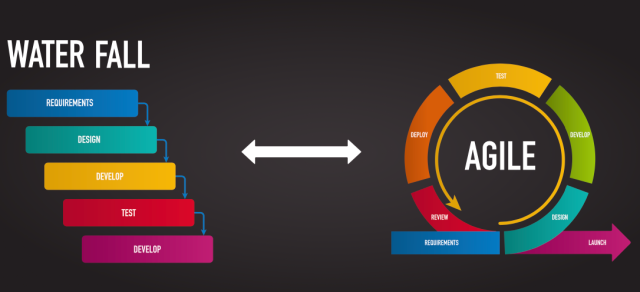

隨著敏捷方法的建立提高了生產力和質量,業界對于硬件設計的興趣正在增長。

盡管如此,人們普遍認為硬件領域的成功依舊是有限的。現實可能比想象要好一些,因為硬件中的某些敏捷性趨勢沒有明確標記。

例如,我們看到越來越多的努力將IP級設計和驗證與SoC級設計和驗證分離。在這種情況下,不同的IP團隊都從SoC項目的“列車模型”上以異步的方式運行,當完成SoC設計時可以選擇任何版本的IP。

雖然這種方法沒有被貼上敏捷的標簽,但這種方法確實符合敏捷哲學。

敏捷設計發展的最大阻力——算力

芯片流片的高成本和流片后無法更改設計通常被認為是敏捷方法不能很好地映射到到硬件設計的關鍵原因。但是,流片后無法敏捷并不一定意味著我們不能在流片前更加敏捷。

在硬件設計中采用敏捷性設計最大阻力之一是硬件驗證的復雜性。測試軟件程序只需要執行該程序所需的計算,當然測試會全速運行。

測試硬件設計需要一個模擬器程序,該程序可以在軟件中模擬芯片設計在硬件中制造時的行為。這個模擬器程序的計算非常昂貴,但其執行速度比它正在模擬的真實芯片的速度慢數千倍。

設計硬件的公司在測試其設計時會受到計算能力的限制。幾家支持系統設計的公司都提供特殊的仿真加速器,它們使用專為仿真加速而設計的專用處理器或FPGA。這些系統的模擬速度比通用服務器上的模擬快數百倍,它們的成本也相應地更加昂貴。因此,設計團隊發現他們在這些平臺上的計算資源同樣有限。

敏捷設計需要持續集成和測試,不僅是單元級別,整個系統級別同樣如此。如果測試受限于計算能力,那么敏捷設計需要更高的計算效率,尤其是在系統級別。例如,一個典型的現代SoC需要在數千臺機器的服務器群上進行長達五天的連續計算來完成一組基本的完整芯片測試。

在如此極端的計算背景下,設計團隊如何才能讓芯片設計變得更加敏捷?

解決敏捷計算挑戰的兩個方法

有兩個關鍵方法可以推動解決敏捷硬件設計中的計算障礙:通過參數化減少設計規模和通過計算物流(雷鋒網注,計算物流涉及使用計算和高等數學來規劃和實施大型和復雜的任務。計算物流應用于許多領域,包括貨物、服務和相關信息從原產地到消費地的流動和儲存。)減少測試規模。

第一,參數化。復制在SoC設計中越來越普遍,無論是IP級復制(如多核 CPU),還是架構級復制(如GPU中的著色器內核或AI加速器中的MAC節點)。通過利用參數化,可以在某種形式的參數化下將更多相似但不同的事物融合在一起,從而顯著增強復制的范圍。

設計中的復制越多,自動生成設計的縮減配置的可能性就越大,這些配置更小但對測試仍然有意義。參數化的使用越復雜,在SoC級別最小化用于測試特定功能的設計尺寸就越靈活。

System Verilog等主流硬件描述語言(HDL)已經很好地支持復制和參數化,但可以通過采用更高級的語言作為HDL生成器來進一步啟用它們。例如,SystemC、Matlab、Python或Chisel。與分離IP和SoC級設計的趨勢一樣,采用高級語言進行硬件設計也出現了類似的趨勢。

至于計算物流,如果我們在敏捷設計方法下持續集成和測試,那么每次集成和測試都是對之前的集成和測試的增量。對于給定的增量設計更改,計算邏輯意味著自動確定最佳設計配置、測試集和測試配置,以便以最低的計算成本提供良好的驗證質量。

可以將其視為一類新的EDA工具——一個引擎在完整的驗證流程中控制所有其它引擎。

我們看到了通過計算物流提高驗證計算效率的巨大潛力,特別是如果期待異構的、基于云的未來,在廣泛的模擬和仿真平臺上可以對無限使用容量進行計費。正如計算物流改變了UPS和FedEx等運輸公司的包裹吞吐量一樣,它也可以改變硬件設計中的驗證吞吐量。

總結

硬件設計已經變得更加敏捷,但仍有很大的改進空間。與軟件驗證相比,這種改進的一個關鍵障礙是硬件驗證的巨大計算成本。

通過利用復制、參數化和高級語言作為HDL生成器,我們可以最大限度地減少測試中的設計尺寸。通過采用計算物流,我們可以最大限度地減少測試工作量并進一步優化測試中的設計尺寸,尤其是在支持云的未來,以及基于使用無限制驗證計算的可用性。

本文作者 Paul Cunningham 是 Cadence Design Systems 系統和驗證組的高級副總裁兼總經理。

本文轉自雷鋒網,如需轉載請至雷鋒網官網申請授權。