小芯片終于迎來統一標準:英特爾、臺積電等巨頭共同坐鎮

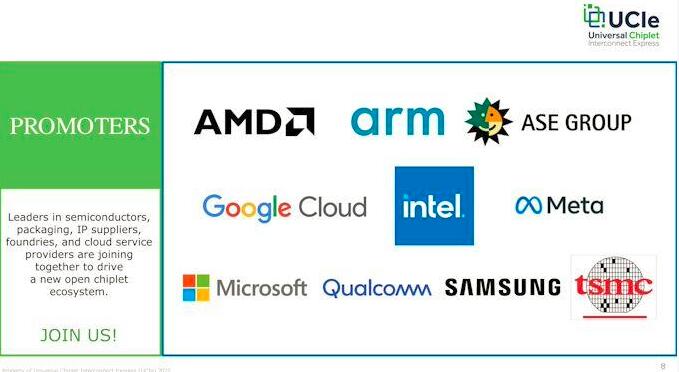

3月3日,全球知名芯片制造商英特爾、臺積電、三星聯手芯片封測龍頭日月光,攜AMD、Arm、高通、谷歌、微軟、Meta等科技行業巨頭推出了一個全新的通用芯片互連標準:通用小芯片快連(UCle)。

該協議專為小芯片(chiplet)而設置,旨在為小芯片互連制定一個新的開放標準,簡化相關流程,并且提高來自不同制造商的小芯片之間的互操作性。該標準下,芯片制造商可以在合適的情況下混合構建芯片。

什么是小芯片?SoC的掘墓人,摩爾定律的“續命丹”

近年來,隨著探索先進制程工藝的成本不斷提高,摩爾定律日漸走向失效。芯片制造行業的頭部廠商一直都在延續摩爾定律的道路上艱難求索。而小芯片,就是這其中的一條道路。

摩爾定律逐漸失效的原因是光掩模限制了單個芯片的最大尺寸,芯片制造商和設計者不得不用多個芯片來實現功能。有些情況下,甚至是多個芯片提供相同的功能。這要求芯片必須完成小型化。

此前廠商一直使用SoC(片上系統)技術組合不同的模塊。這種技術的優勢在于提高模塊之間通信速度的同時,還能夠做到低功耗、低成本。但近年來突破先進制程工藝的難度和成本都在不斷上升。

一方面,技術突破已經變得尤為艱難,在芯片制造領域深耕多年的英特爾,也在7nm制程技術上遭遇瓶頸。而目前掌握5nm制造技術的三星日前也遭曝光產品良率造假。同時,探索先進制程的成本也在不斷上升。根據IBS首席執行官Handel Jones的說法,設計3nm的芯片成本以及達到了5.9億美元,而此前,設計一個28nm的芯片平均成本僅為4000萬美元。

小芯片,顧名思義,就是用多個小芯片封裝在一起,用die-to-die(裸片對裸片)內部互連技術,組成異構芯片。由于小芯片的單體更小,每片圓晶的利用率得以提高,從而降低成本。并且,由于封裝了多個小芯片,可以根據需要進行靈活組裝,從而降低功耗。

“大餅”逐漸落地,小芯片“野蠻生長”

如今,小芯片技術已經開始從理論走向實踐,在一些頭部廠商的帶領下真正應用到芯片的設計和制造中。當初小芯片技術畫下的名為“用搭積木的方式造芯片”的大餅,如今已經離實現越來越近。

AMD在2019年發布的Ryzen3000系列中部署了基于小芯片技術的Zen2內核;英特爾則發布了集成了47個小芯片的Ponte Vecchio。我們可以看到,無論是將單片CPU拆分,還是將大量小芯片集成封裝,小芯片技術都已經走出實驗室,應用到了實際生產中。

但小芯片技術要走向成熟,還需要面對諸多挑戰。

在小芯片技術中,各裸片互連必須考慮到互連接口和協議。在設計中必須要考慮到工藝制程、封裝技術、系統集成、擴展等諸多復雜因素。同時,還需要滿足不同領域對信息傳輸速度、功耗等方面的要求。這使得小芯片的設計過程變得非常復雜,而其中橫在小芯片面前的最大難關來自于沒有統一的協議。

Marvell曾經在2015年推出了MoChi架構這一小芯片模型。此后Marvell就陷入了選擇接口的困難中。根據Marvell的網絡CTO Yaniv Kopelman說,由于不想堆高封裝成本或是被單個供應商綁定,他們不想使用內插器或者InFO類型的封裝。另外,使用小芯片的時候必須在中間劃分IP,但在哪里劃分以及如何開發架構也對最終產品的實現提出了挑戰。

Yaniv Kopelman總結到:“在演示中構建IP很容易,但從演示走向生產還有很長的路要走。”

在過去五年內,小芯片一直是芯片設計行業中一顆耀眼的新星。越來越多的廠商開始使用小芯片,這使得它越來越普遍。制造商們希望小芯片解決芯片制造目前面臨的制造成本、擴展性等多方面的問題。

但由于缺少統一的標準,小芯片此前的協議如同混亂的“春秋戰國”。這樣的情況下,芯片制造商們無法實現他們的終極構想:連通不同架構、不同制造商生產的裸片,根據不同場景進行定制。

“春秋戰國”終結,UCle1.0只是開始

小芯片技術一直在呼喚一個統一的標準。

英特爾擁有高級接口總線技術(AIB),這是一種芯片到芯片的PHY級標準,采用模塊化設計,具有IP模塊庫。并且,英特爾免費提供了AIB接口許可,以推廣小芯片生態。

同時能夠在小芯片上使用的并行接口標準還有臺積電的LIPINCON、OCP的BoW等。

僅僅是物理層中的并行接口標準,就已經如此多樣,這給制造廠商帶來不小麻煩,使得小芯片生態始終難以推廣。

芯片行業正集體呼喚一個能夠使小芯片終結“春秋戰國”時代,做到“車同軌,書同文”的統一標準。

英特爾似乎一直是都是那個最有機會掃清小芯片發展障礙的公司。英特爾新任總裁Pat自2021年上任以來一直強調英特爾要走IDM2.0的道路,在芯片制造上繼續深耕的同時還要具有更高的開放性,這正好與小芯片技術的理念不謀而合。

在2月18日的英特爾投資者大會上,英特爾宣布將為選擇其旗下IFS服務代工的客戶提供x86架構和其他類型內核混搭的可能性,這以一過程中可能就會用到小芯片技術。同時英特爾還在該大會上披露正在致力于打造一個“開放、可選擇、值得信賴”的開放生態圈。這一藍圖似乎就是如今英特爾牽頭制定的UCle1.0標準的伏筆。實際上,UCle1.0標準的初始版本就來自英特爾,該標準一定程度上借鑒了英特爾曾經提出的AIB標準。

如今這個巨頭們共同站臺的UCle1.0標準帶來的并不是技術革新,而是技術的標準化。這使得各廠商在使用小芯片時終于有了共同的規則。

UCle規范包括了物理層和協議層。在物理層上規定了小芯片之間互相通信的電氣信號標準、物理通道數量和支持的凸塊間距。而在協議層上該規范定義了覆蓋在這些信號上的更高級別協議。這一規范將使得所有在設計和制造中遵守它的小芯片能夠互連。

UCle1.0根據復雜度的不同設計了“標準封裝”和“高級封裝”兩個級別的標準。

“標準封裝”為使用傳統有機襯底的低帶寬器件設計,這些部件將使用16條數據通道、遵循100μm+的凸塊間距和擴展通道長度。這實際上就是在非常近的距離上在一個當代PCle鏈路中鏈接兩個設備。

“高級封裝”中則涵蓋了EMIB和InFO等技術。并要求25μm~55μm之間的凸塊間距,同時由于更高的密度和更短的通信范圍,數據通道的數量將是標準封裝的四倍。如果使用這種標準,每秒可在1mm芯片邊緣通過的數據量可以達到1.3TB。

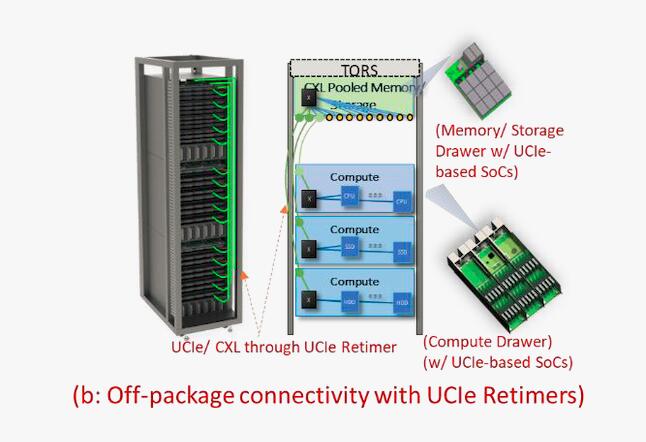

不僅如此,UCle實際上還可以在小芯片以外找到自己的舞臺。實際上,雖然UCle的重點是為小芯片提供片上互連的統一標準,但該標準中包含了外部互連的規定。

只要芯片制造商愿意,該規范允許使用重定時器在協議級別完成更遠距離的傳輸。雖然這使得延遲和功率隨著距增加,但UCle的推廣者設想服務器用戶可能需要這種長距離上的小芯片互連。

雖然UCle1.0規范的出現終于解決了困擾在小芯片領域很長時間的規范混亂問題,但它仍然只是一個開始。有人將這一標準稱為“起點標準”,這是由于該標準指定義了小芯片設計中的物理層和協議層,這僅僅是小芯片設計中四個方面中的兩個。行業龍頭們仍然在尋求小芯片形狀要素等方面的統一,以真正實現構建可混合搭配的小芯片生態系統。

另一方面,UCle1.0標準基本只針對2D和2.5D芯片封裝做出了定義,而更先進的3D封裝相關標準還需要等待更新。

UCle聯盟的成員們將要開發下一代UCle技術,新協議將會更加完善。雖然UCle聯盟已經匯集了在芯片設計和制造領域的幾大龍頭,可以稱得上是群星薈萃。但要想這一標準走的更遠,以至于實現芯片制造商們搭建完善的小芯片生態的構想,還需要更多人參與到這一聯盟的建設中來。

本文轉自雷鋒網,如需轉載請至雷鋒網官網申請授權。