AVX512惹麻煩 英特爾大小核給AMD上了一課 Zen5銳龍吸取教訓

英特爾2021年推出的12代酷睿Alder Lake處理器應該是20多年來桌面x86最大的一次變革,首次引入了異步架構,CPU由大小核兩種組成,英特爾的官方說法是P核、E核。

P核負責高性能任務,E核主要是高密度任務,這點跟Arm的小核偏向省電不同,這也是Intel不愿意稱之為大小核的原因,因為E核的性能也不弱。

P+E核的引入讓英特爾獲得了性能、多核、成本及面積等多方面的優勢,而且4個E核面積才相當于1個P核,因此輕松堆出12核以上的產品,這讓AMD苦不堪言。

AMD什么時候跟進大小核架構還不確定,但是AMD倒是明確從Intel的教訓中學到了一課,那就是英特爾在AVX512指令集上的做法,E核是不支持的,P核支持,但是為了兩個核心同步,英特爾最終封殺了AVX512指令集,這也引發網友不滿。

臺北電腦展2023期間,AMD副總裁、客戶端渠道業務總經理David McAfee在采訪中就談到了這一點,表示設計兩種不同ISA指令集及IPC性能的性能核、效能核不一定是正確的方法,這會帶來更多的復雜性,AMD已經研究了核心設計的不同選項,(英特爾的做法)不是AMD正在使用的方法。

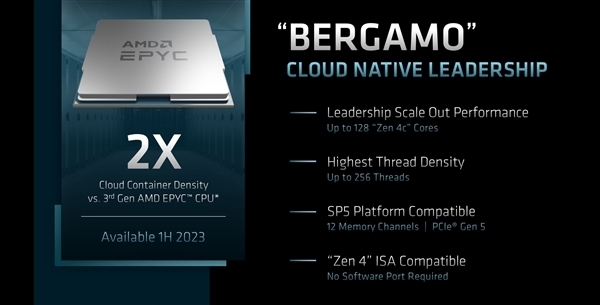

他說的AMD做法指的就是Zen4與Zen4C核心的區別,后者是AMD 128核處理器Bergamo使用的小核心,基于Zen4核心改進的,但指令集及IPC是一樣的,主要是精簡了緩存結構以減少核心面積。

AMD認為這種大小核的設計更好,Windows系統的調度優化等都是很成熟的,不用考慮指令集及工作負載的不同。

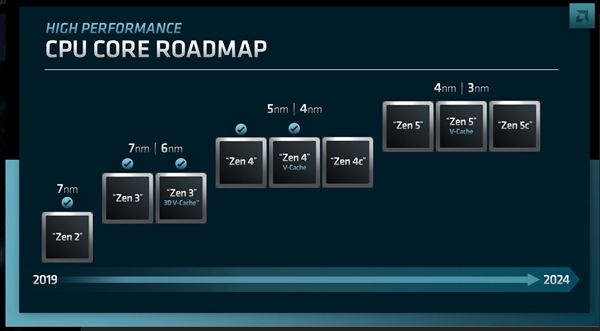

不過AMD的大小核并沒有混搭,Bergamo上全是Zen4C核心,銳龍桌面處理器用上大小核混搭架構至少要等Zen5了,會有Zen5及Zen5C兩種核心,AMD已經從英特爾的教訓中學了一課,Zen5大小核是不會出現指令集不同這樣的尷尬了。