L1 L2 L3 Cache到底放在哪里好呢?

本文轉(zhuǎn)載自微信公眾號(hào)「虛機(jī)」,作者cloud3 。轉(zhuǎn)載本文請(qǐng)聯(lián)系虛機(jī)公眾號(hào)。

我是cloud3,前段時(shí)間寫(xiě)了幾篇關(guān)于高速緩存的文章,很多朋友加我好友也聊了不少。今天我們看看Cache的發(fā)展歷史,這L1 L2 L3 Cache一開(kāi)始是放哪里的?

好了,今天不講原理,只看歷史(intel):

無(wú)需Cache

Cache(高速緩存)的發(fā)展是計(jì)算歷史上最重要的技術(shù)之一。幾乎所有的現(xiàn)代CPU內(nèi)核都設(shè)計(jì)有高速緩存。但是一開(kāi)始CPU是沒(méi)有Cache的,因?yàn)樵缙诘腃PU主頻很低,甚至都沒(méi)有內(nèi)存的頻率高,所以無(wú)需Cache,CPU直接讀寫(xiě)內(nèi)存。

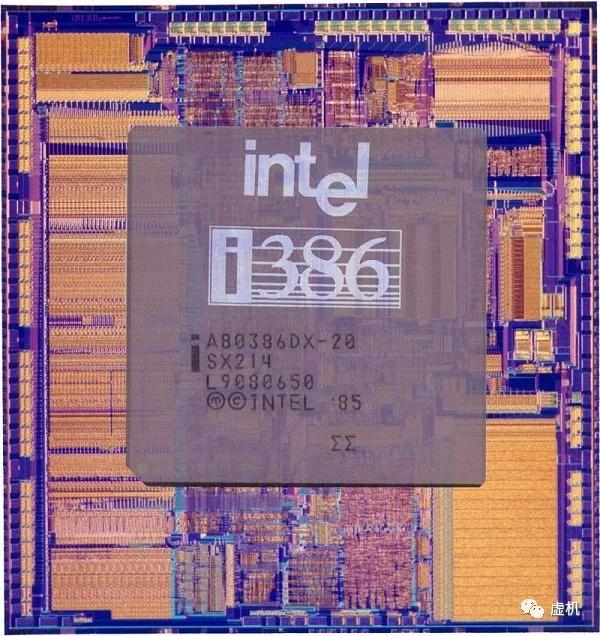

外部Cache出現(xiàn)

從80386開(kāi)始CPU主頻開(kāi)始遠(yuǎn)高于內(nèi)存頻率。80386DX為25MHz,一個(gè)總線周期為2拍80ns,當(dāng)時(shí)已沒(méi)有速度相匹配的DRAM可用。在馮諾依曼結(jié)構(gòu)下,CPU的訪存速度就成了瓶頸,為了能夠加速內(nèi)存訪問(wèn),Intel主板上增加了外部Cache來(lái)配合80386運(yùn)行,當(dāng)時(shí)的Cache都是Write-Through的。這就是最初的Cache。

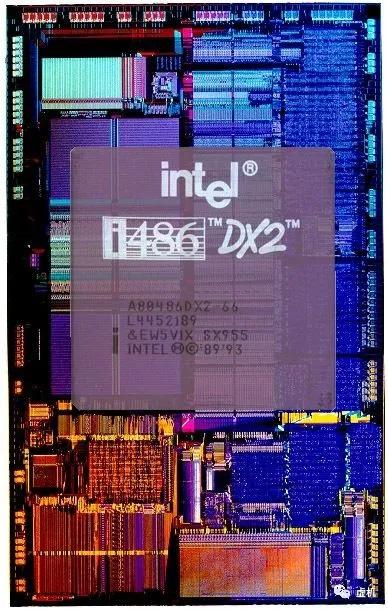

內(nèi)部L1 Cache

80486開(kāi)始Cache被設(shè)計(jì)在了在CPU內(nèi)部,加入了8KB的L1 Cache,但是不分指令和數(shù)據(jù)Cache,同時(shí)也可以使用CPU外部主板上的Cache,即L2 Cache,大小從128KB到256KB不等。80486內(nèi)部的Cache是4路組相聯(lián)的設(shè)計(jì),并且增加了Write-back的Cache屬性。

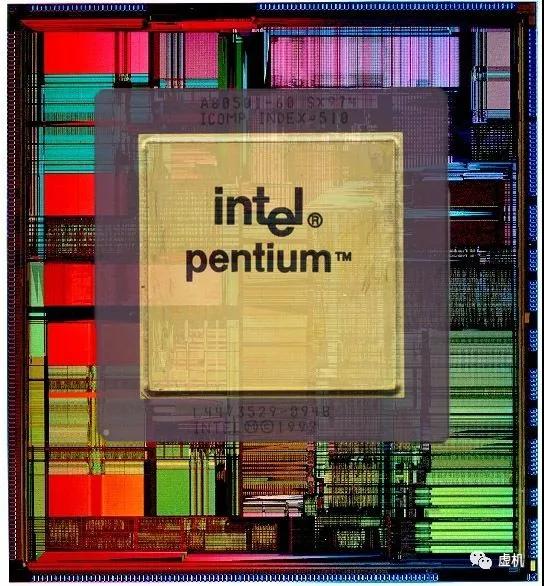

指令和數(shù)據(jù)Cache分開(kāi)

到了80586/Pentium-1,Intel采用了雙路執(zhí)行的超標(biāo)量結(jié)構(gòu),有2條并行整數(shù)流水線,需要對(duì)數(shù)據(jù)和指令進(jìn)行雙重訪問(wèn),為了使訪問(wèn)互不干涉,于是L1 Cache被一分為二,分為指令Cache和數(shù)據(jù)Cache,都是8KB大小。這就是iCache和dCache的鼻祖了。另外此時(shí)的一致性協(xié)議采用了MESI緩存一致性協(xié)議。

但是此時(shí)L2 Cache還是外部的,后面的Pentium Pro才把L2放到CPU內(nèi)部,到此為止,就確定了現(xiàn)代緩存的基本模式,并且一直沿用至今。

雙核上的L2 Cache

來(lái)到雙核時(shí)代之后,Intel雙核心CPU陸續(xù)推出了Pentium D、Pentium EE、Core Duo,其中Pentium D、Pentium EE的CPU內(nèi)部?jī)蓚€(gè)內(nèi)核具有互相獨(dú)立的二級(jí)緩存,不是共享的呀。所以兩個(gè)CPU核之間的緩存數(shù)據(jù)同步是依靠北橋芯片上的仲裁單元通過(guò)前端總線在兩個(gè)核心之間傳輸來(lái)實(shí)現(xiàn)的,延遲還比較大。

多核共享L2 Cache

雙核CPU中的Core Duo在二級(jí)緩存上有了巨大突破,就是兩個(gè)核共享2MB的二級(jí)緩存,使用Intel的“Smart cache”共享緩存技術(shù),實(shí)現(xiàn)了真正意義上的緩存同步,極大發(fā)揮了二級(jí)緩存的作用。

現(xiàn)在Cache

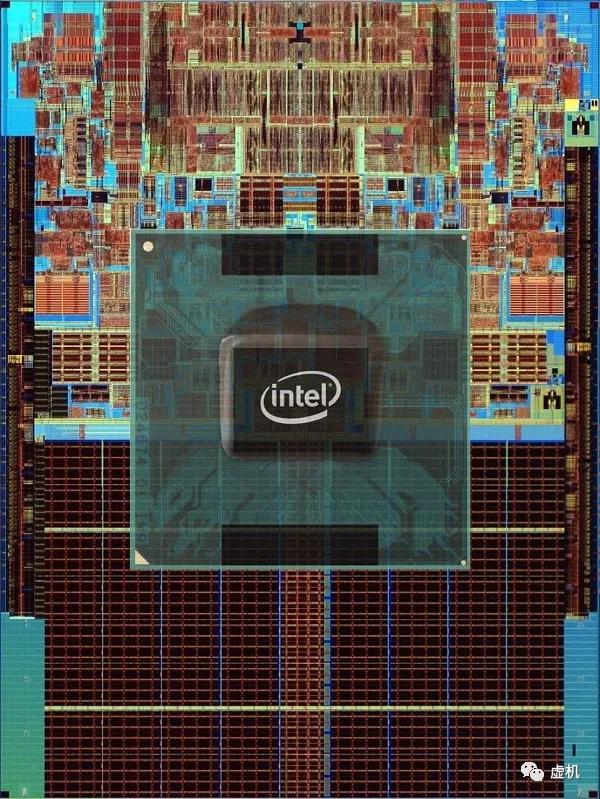

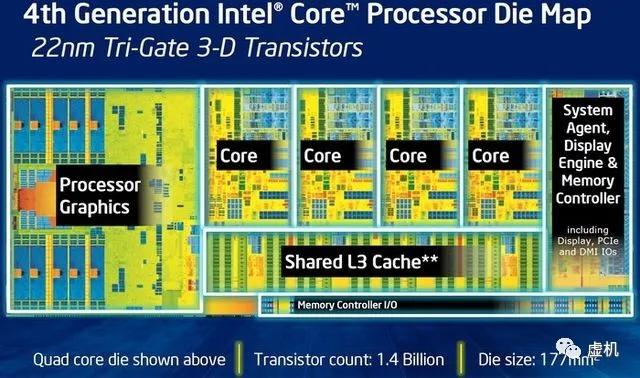

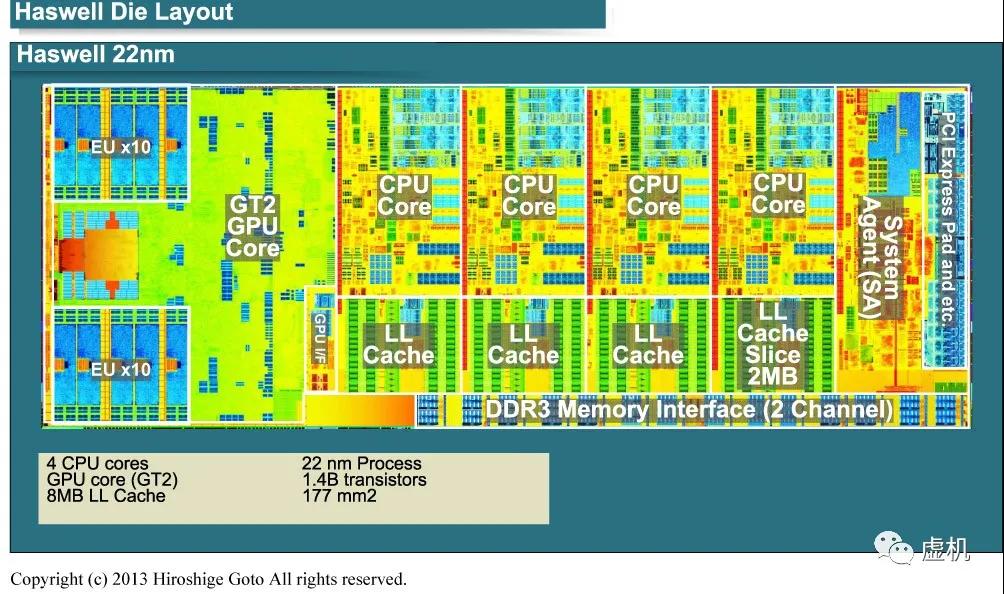

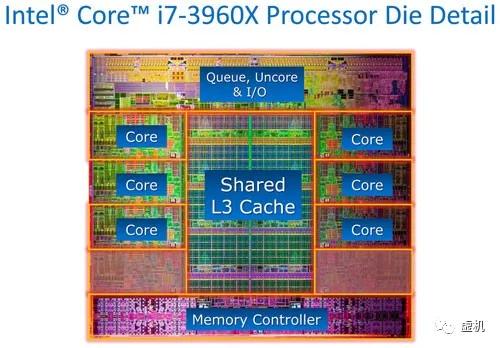

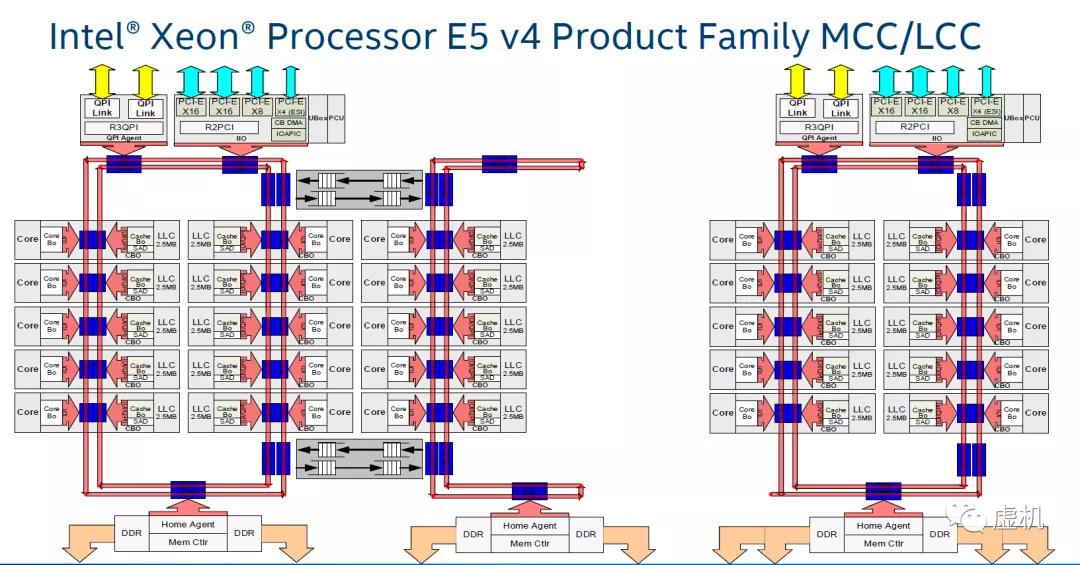

現(xiàn)在CPU都有L3 Cache,一般是多核共享模式,而L2則被每個(gè)核單獨(dú)占據(jù)。這時(shí)L2也叫做MLC(Middle Level Cache),而L3被叫做LLC(Last Level Cache)。最后我們看看幾個(gè)典型的Cache設(shè)計(jì)圖:

了解了高速緩存的歷史基本就能窺出一點(diǎn)CPU的設(shè)計(jì)歷史。