教你精確計算 I2C 上拉電阻阻值

I2C 總線能掛多少設備?

理論上:

7-bit address :2 的 7 次方,能掛 128 個設備。

10-bit address :2 的 10 次方,能掛 1024 個設備。

當然,要把預留設備地址去除,7 bit 協議規定了 8個預留地址,普通廠商不可以使用。保留地址如下:

但是 I2C 協議規定,總線上的電容不可以超過 400pF。管腳都是有輸入電容的,PCB 上也會有寄生電容,所以會有一個限制。實際設計中經驗值大概是不超過 8 個器件。

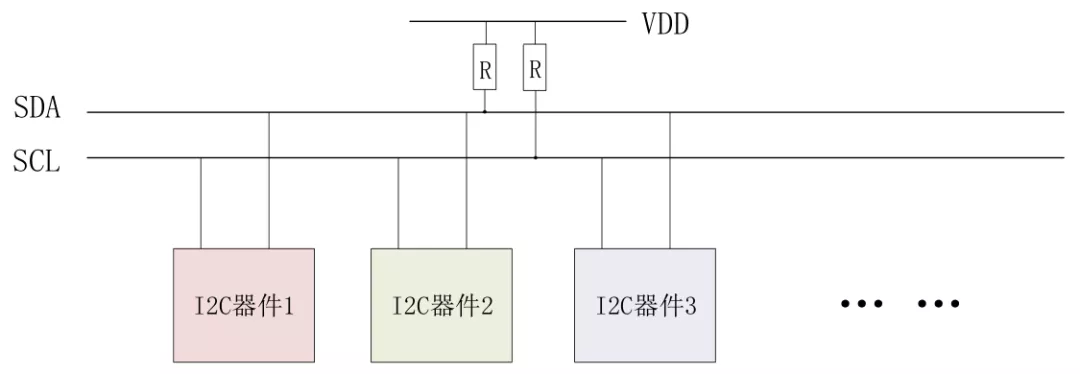

總線之所以規定電容大小是因為,I2C 使用的 GPIO 為開漏結構,開漏結構無法輸出高電平,要求外部有上拉電阻拉高。電阻和總線電容產生了一個 RC 延時效應,電容越大信號的邊沿就越緩,有可能帶來信號質量風險。

傳輸速度越快,信號的窗口就越小,上升沿下降沿時間要求更短更陡峭,所以 RC 乘積必須更小。

I2C 架構

我們知道 I2C 有不同的速度模式,標準(100KHz)、快速(400KHz)、快速plus(1MHz)、高速(3.4MHz)。

Vdd 可以采用 5V、3.3V、1.8V 等,電源電壓不同,上拉電阻阻值也不同。

一般總線上認為,低于 0.3Vdd 為低電平,高于 0.7Vdd 為高電平。

上拉電阻計算

1、上拉電阻過小,總線上電流增大,端口輸出低電平增大。

2、上拉電阻過大,上升沿時間增大,方波可能會變成三角波。

因此計算出一個精確的上拉電阻阻值是非常重要的。

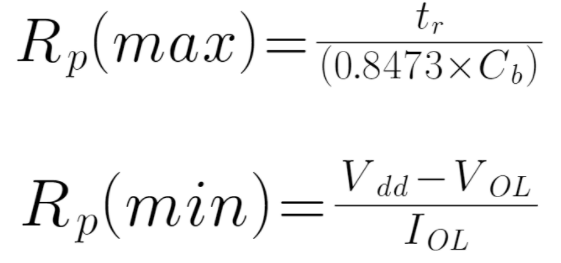

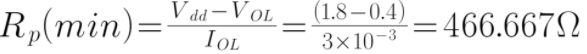

計算上拉電阻的阻值,是有明確計算公式的:

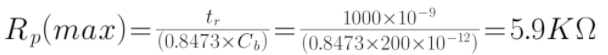

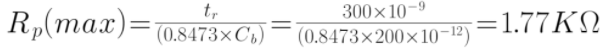

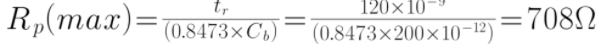

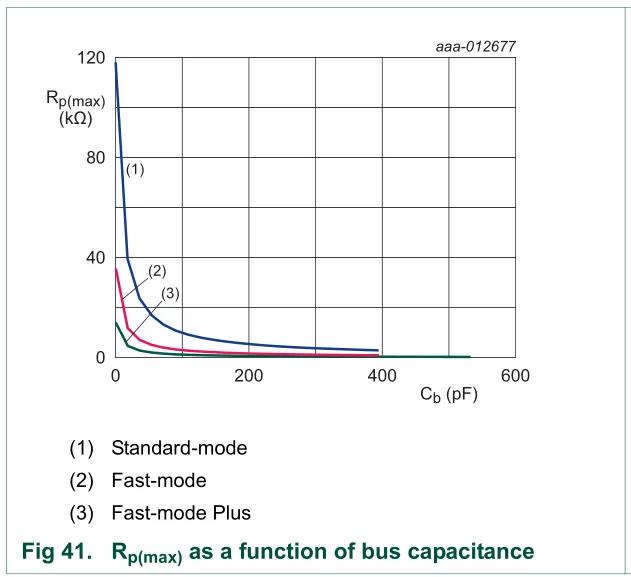

最大電阻和上升沿時間 tr 、總線電容 Cb 、標準上升沿時間 0.8473 有關。

最小電阻和電源 Vdd 電壓、GPIO 口自己最大輸出電壓 Vol、 GPIO口自己最大電流 Vol 有關。

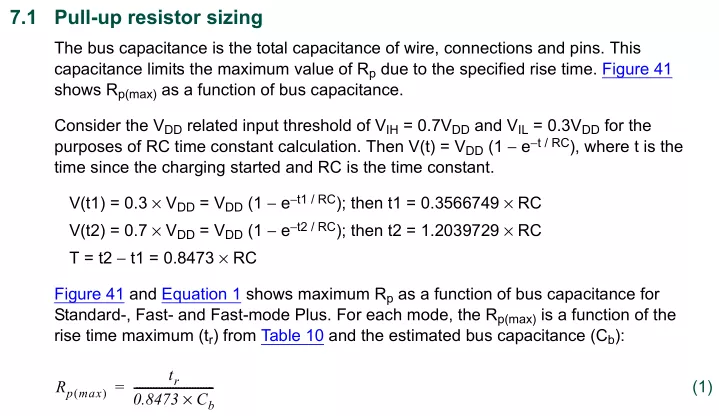

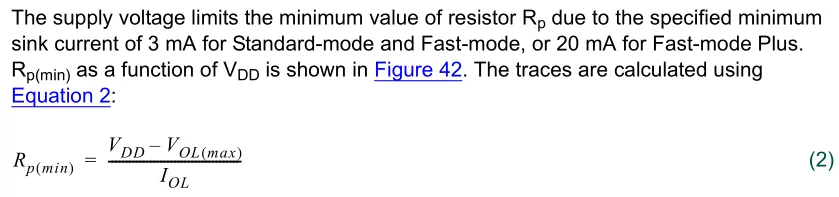

查《I2C-bus specification and user manual.pdf》7.1節:

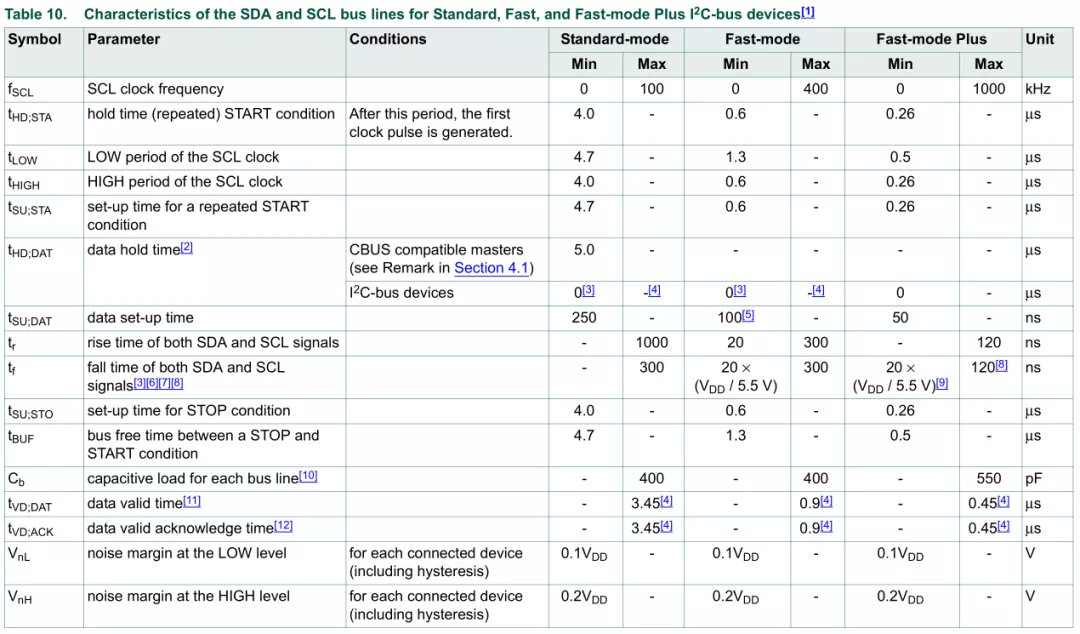

查《I2C-bus specification and user manual.pdf》表10:

由上表可知:

1、標準模式:0~100KHz,上升沿時間 tr = 1us

2、快速模式:100~400KHz,上升沿時間 tr = 0.3us

3、高速模式:up to 3.4MHz,上升沿時間 tr = 0.12us

由此公式,假設 Vdd 是 1.8V 供電,Cb 總線電容是200pF(雖然協議規定負載電容最大 400pF,實際上超過 200pF 波形就很不好,我們以 200pF 來計算)

標準模式 :

快速模式:

高速模式:

最小電阻(Vdd越大,上拉電阻就要越大):

note:高速模式下,電源電壓一般采用 1.8 V,不會采用 3.3V,因為如果用 3.3V 計算你會發現最小電阻比最大電阻大。

大家在不同速率采用的電阻一般有以下幾種:1.5K、2.2K、4.7K。

一般大家采用 I2C 使用標準模式即可 ,也就是 100KHz,推薦上拉電阻是 4.7K,當然大家可以用示波器看傳輸波形,適當調整。

結論:I2C 上拉電阻阻值和電源電壓、傳輸速度、總線電容(負載因素)都有關系,大家根據自己的板子計算一下即可,選取最優電阻阻值,從而獲得最優傳輸波形。

最大電阻 Rp 和總線電容 Cb 關系圖:

note:建議總線電容維持在 100pF 以下。