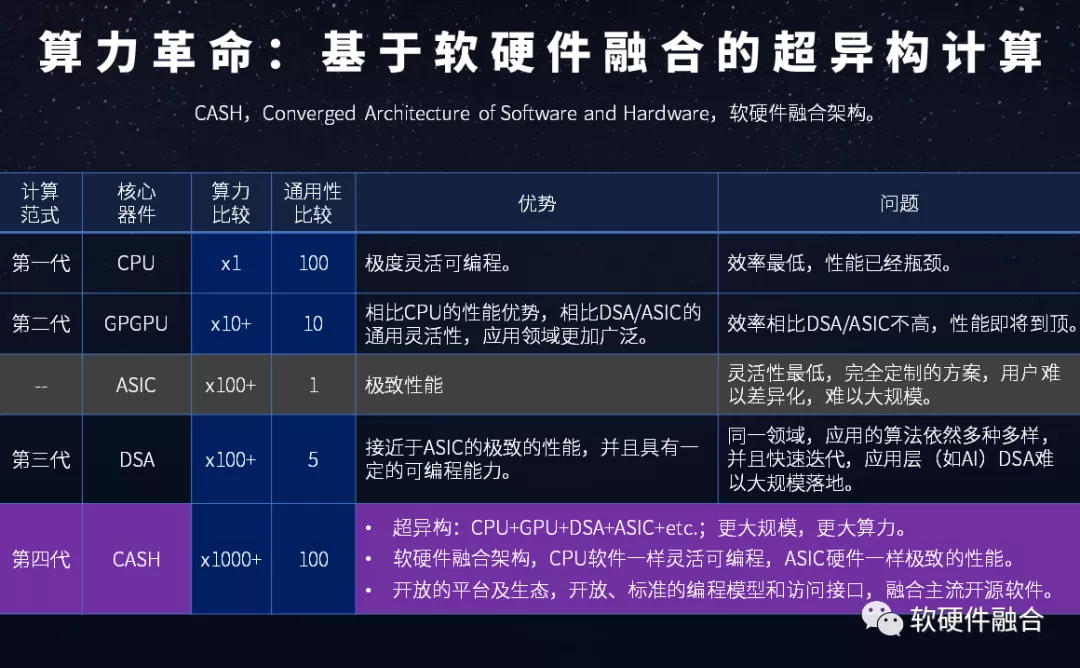

第四代算力革命:基于軟硬件融合的超異構計算

編者按

日前,國家發改委等四部門聯合發布《全國一體化大數據中心協同創新體系算力樞紐實施方案》,提出在京津冀、長三角、粵港澳大灣區、成渝以及貴州、內蒙古、甘肅、寧夏建設全國算力網絡國家樞紐節點,啟動實施“東數西算”工程,構建國家算力網絡體系。

算力,成為整個數字信息社會發展的關鍵。通過“東數西算”能緩解一些問題,但沒有根本解決問題:當前要想提升算力,更多的是靠“攤大餅”的方式構建更加規模龐大并且低能耗的現代化數據中心。

這是算力提升的Scale out(增大規模),那么,我們如何能夠做到算力的Scale up(提升單個計算節點的性能)?或者說,我們如何顯著(數量級)的提高單個處理器的性能?

當前,算力成為制約信息技術更加蓬勃發展的最核心問題:

- CPU靈活性好,但效率最低,并且已經性能瓶頸;

- GPU具有一定的靈活性,但效率相比DSA仍有差距,并且在可見的未來很快會面臨和CPU一樣的性能瓶頸問題。

- DSA在極致性能的情況下,提供了一些靈活性。但面對的領域(Domain)應用多種多樣并且快速變化,一直沒能實現DSA芯片的大規模落地。

我們需要構建新一代的創新計算范式,相比當前,要把算力至少再提升1-2個數量級,并且能夠提供非常好的易用編程能力,來持續應對未來10年的更加復雜系統的算力需求爆炸的挑戰。

注:本文想法還比較粗糙,拋磚引玉,期待更多的討論,未來會優化更新。

一、第一代:CPU

1.1 指令集軟硬件解耦,CPU性能狂飆,軟件蓬勃發展

指令集,是軟硬件的媒介。CPU是最靈活的,原因在于運行于CPU指令都是最基本的加減乘除外加一些訪存及控制類指令,就像積木塊一樣,我們可以隨意組合出我們想要的各種形態的功能,形成非常復雜并且功能強大的程序,或者稱為軟件。

CPU最大的價值在于提供并規范了標準化的指令集,使得軟件和硬件從此解耦:

硬件工程師不需要關心場景,只關注于通過各種“無所不用其極”的方式,快速的提升CPU的性能。

而軟件工程師,則完全不用考慮硬件的細節,只關注于程序本身。然后有了高級編程語言/編譯器、操作系統以及各種系統框架/庫的支持,構建起一個龐大的軟件生態超級帝國。

通過標準化指令集,達到軟硬件解耦,并且互相向前兼容(軟件向前兼容之前的硬件,硬件向前兼容之前的軟件)。這樣,CPU的硬件設計者,可以不用考慮上層的業務到底是什么,也即不關心通過指令組合出的程序到底是干什么用的。只需要關心,我設計的CPU性能如何的好,可以實現更高的IPC(Instructions per Cycle)和更高的頻率。

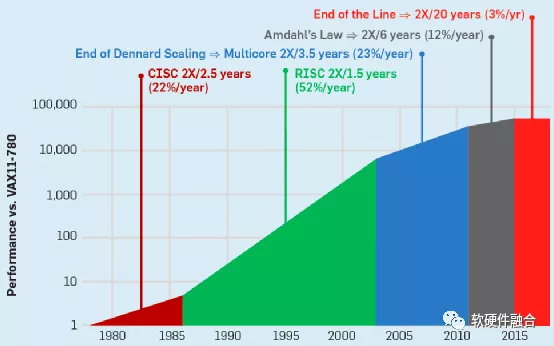

圖1. 歷年CPU性能提升對比

從圖1中,可以看到,在差不多40年的時間里,CPU的整體性能提升接近50000倍。一方面,這有賴于處理器架構的翻天覆地變化,也有賴于半導體工藝的進步。另一方面,更有賴于通過標準化的指令集,使得CPU平臺的硬件實現和軟件編程完全解耦,沒有了對方的掣肘,軟件和硬件均可以完全的放飛自我。

一方面是CPU性能狂飆,另一方面,則是軟件逐漸發展成了一個超級的生態帝國。從各種數以百萬級使用者的高級編程語言,到廣泛使用在云計算數據中心、PC機、手機等終端的智能操作系統,再到各種專業的數據庫、中間件,以及云計算基礎的虛擬化、容器等。上述這些軟件都是基礎的支撐軟件,是軟件的“冰山一角”,而更多的則是各種用戶級的應用軟件,系統級和應用的軟件,共同組成了基于CPU的軟件超級生態。

1.2 摩爾定律失效,CPU性能瓶頸,制約軟件的發展

圖2. CPU性能提升的五個階段

圖2和上一節的圖1是一致的,圖2主要是明確展示了五個發展階段:

- CISC階段。在上世紀80年代,以Intel和AMD的x86架構為典型代表的CISC架構CPU開啟了CPU性能快速提升的時代,CPU性能每年提升約25%(圖中22%數據有誤),大約3年性能可以翻倍。

- RISC階段。隨后,CISC系統越來越復雜,有很多設計資源花在了不經常使用的指令實現上。隨后,RISC證明了“越精簡,越高效”。隨著RISC架構的CPU開始流行,性能提升進一步加快,每年可以達到52%,性能翻倍只需要18個月。

- 多核階段。單核CPU的性能提升越來越困難,開始通過集成更多CPU核并行的方式來進一步提升性能。這一時期,每年性能提升可以到23%,性能翻倍需要3.5年。

- 多核整體性能遞減階段。隨著CPU核集成的數量越來越多,阿姆達爾定律證明了處理器數量的增加帶來的收益會逐漸遞減。這一時期,CPU性能提升每年只有12%,性能翻倍需要6年。

- 性能提升瓶頸階段。不管是從架構/微架構設計、工藝、多核并行等各種手段都用盡的時候,CPU整體的性能提升達到了一個瓶頸。如圖,從2015年之后,CPU性能每年提升只有3%,要想性能翻倍,需要20年。

二、第二代:GPU

2.1 GPGPU,通用的并行計算平臺

GPU,Graphics Processing Units,圖形處理單元。顧名思義,GPU是主要用于做圖形圖形處理的專用加速器。GPU內部處理是由很多并行的計算單元支持,如果只是用來做圖形圖像處理,有點“暴殄天物”,其應用范圍太過狹窄。

因此把GPU內部的計算單元進行通用化重新設計,GPU變成了GPGPU。到2012年,GPU已經發展成為高度并行的眾核系統,GPGPU有強大的并行處理能力和可編程流水線,既可以處理圖形數據,也可以處理非圖形數據。特別是在面對SIMD類指令,數據處理的運算量遠大于數據調度和傳輸的運算量時,GPGPU在性能上大大超越了傳統的CPU應用程序。現在大家所稱呼的GPU通常都指的是GPGPU。

圖3. NVIDIA圖靈GPU架構

2018年,NVIDIA發布了最新一代的GPU架構——圖靈架構。基于圖靈架構的GPU提供PCIe 3.0來連接CPU主機接口,提供千兆的線程引擎來管理所有的工作。另外,圖靈架構支持通過兩路x8的NVLink接口實現多GPU之間的數據一致性訪問。

如圖3,圖靈架構GPU的核心處理引擎由如下部分組成:6個圖形處理簇(GPC);每個GPC有6個紋理處理簇(TPC),共計36個TPC;每個TPC有2個流式多核處理器(SM),總共72個SM。每個SM由64個CUDA核、8個Tensor核、1個RT核、4個紋理單元,總計有4608個CUDA核、576個Tensor核、72個RT核、288個紋理單元。

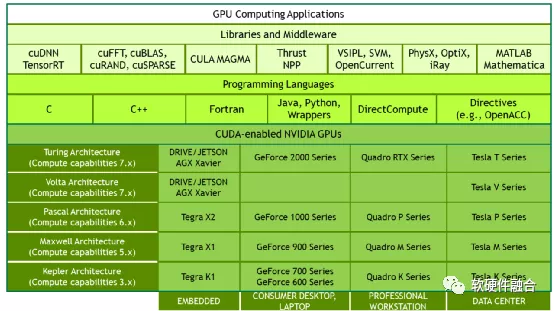

2.2 CUDA,NVIDIA GPU成功的關鍵

圖4. CUDA框架

2006年NVIDIA推出了CUDA,這是一個通用的并行計算平臺和編程模型,利用NVIDIA GPU中的并行計算引擎,以一種比CPU更高效的方式解決許多復雜的計算問題。CUDA提供了開發者使用C++作為高級編程語言的軟件環境。也支持其他語言、應用程序編程接口或基于指令的方法,如FORTRAN、DirectCompute、OpenACC。

CUDA是NVIDIA成功的關鍵,它極大的降低了用戶基于GPU并行編程的門檻,在此基礎上,還針對不同場景構建了功能強大的開發庫和中間件,逐步建立了GPU+CUDA的強大生態。

三、第三代:DSA

3.1 DSA興起

2017年三月,圖靈獎獲得者David Patterson和John Hennessy在其“體系結構的黃金年代”主題演講中,提出了DSA架構。CPU的性能提升走向終結,需要針對特定場景有針對性的定制加速,而DSA則是切實可行的解決方案。DSA是在定制ASIC的基礎上回調,使其具有一定的軟件可編程靈活性。

按照指令的“復雜度”,DSA可以歸屬到ASIC一類。跟CPU、GPU、FPGA以及傳統ASIC相比,DSA具有如下一些特點:

- 跟GPU、FPGA類似,通常的DSA不是圖靈完備的。是面向系統中的計算密集型任務的計算加速,而不是運行整個系統。因此DSA平臺的架構是“CPU+DSA”。

- DSA有簡單的指令集,可以編程,因此是處理器;DSA是針對特定領域定制設計,因此是特殊的一種ASIC。DSA可以看做是通常意義上的ASIC向通用處理的一種回調,增加了ASIC的靈活性。

- DSA應用領域的規模足夠大的話,可以去定制IC芯片,這樣可以覆蓋IC芯片高昂的前期成本;如果規模較小,選擇FPGA實現DSA設計則是一個更好的選擇。

- 架構和邏輯設計需要了解具體的領域和相關算法,而不是僅僅關注架構和設計本身。

- 基于CPU+DSA的異構編程是個非常大的挑戰。

3.2 AI領域DSA案例:谷歌TPU

DSA架構的第一個經典案例是谷歌的TPU。TPU(Tensor Processing Unit,張量處理單元)是Google定制開發的ASIC芯片,用于加速機器學習工作負載。谷歌在2013年進行的一項預測分析顯示,人們每天使用語音識別DNN進行語音搜索三分鐘,這將使數據中心的計算需求增加一倍,而使用傳統的CPU成本非常昂貴。因此,谷歌啟動了一個高優先級項目,即TPU項目,以快速生成用于推理的自研ASIC。目標是將GPU的性價比提高10倍。

圖5. 谷歌TPU 1.0結構框圖

如圖5,顯示了TPU的結構框圖。TPU指令通過PCIe Gen3 x16總線從Host發送到TPU的指令緩沖區。內部模塊通過256字節寬的總線連接在一起。開始在右上角,矩陣乘法單元是TPU的核心,它包含256x256 MAC,可以對有符號或無符號整數執行8位乘加,16位乘積收集在矩陣單元下方的4 MB 32位累加器中。4 MB可容納4096個256元素的32位累加器。矩陣單元每個時鐘周期產生一個256個元素的部分和。

TPU指令設計為CISC(復雜指令集計算機)類型,包括一個重復域。這些CISC類型指令的CPI(Cycles per Instruction,每條指令的平均時鐘周期)通常為10到20。總共大約有十二條指令,主要的五個指令是:

- Read_Host_Memory。將數據從CPU內存讀取到統一緩沖區(UB)中。

- Read_Weights。將權重從權重存儲器讀取到權重FIFO中,作為矩陣單元的輸入。

- MatrixMultiply / Convolve。讓矩陣單元執行矩陣乘法或執行從統一緩存區到累加器的卷積。矩陣運算采用大小可變的B*256輸入,然后將其乘以256x256恒定的權重輸入,然后生成B*256輸出,需要B個流水線周期才能完成。

- Activate。根據ReLU,Sigmoid等選項,執行人工神經元的非線性功能。它的輸入是累加器,其輸出是統一緩沖區。當連接到非線性函數邏輯時,還可以使用芯片上的專用硬件執行卷積所需的池化操作。

- Write_Host_Memory 將數據從統一緩沖區寫入CPU內存。

其他指令包括備用Host內存讀寫、組配置、兩個版本的同步、中斷主機、調試標簽、空指令NOP和停頓Halt。

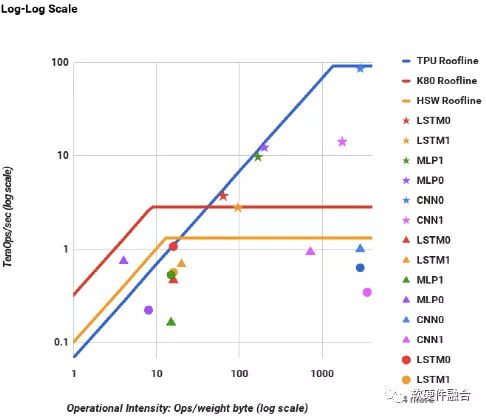

(★代表TPU,▲代表K80 GPU,●代表Haswell CPU)

圖6. CPU、GPU和TPU的Roofline組合圖

如圖6,對于HPC來說,Y軸是每秒浮點運算的性能,X軸是操作強度,用訪問的每個DRAM字節的浮點操作來衡量。峰值計算速率就是Roofline的“平坦”部分,內存帶寬是每秒字節數,因此變成了Roofline的“傾斜”部分。從圖6中,我們可以看到,所有TPU星星均位于CPU和GPU的Roofline之上。從Roofline的平坦部分可以看出,TPU的處理速度比GPU和CPU要快15-30倍。

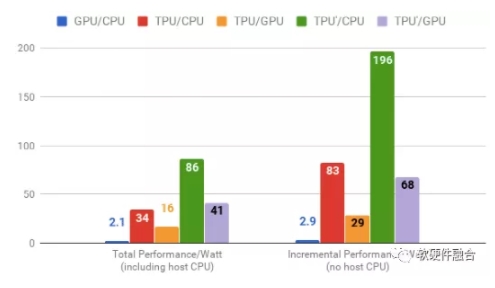

圖7. CPU、GPU和TPU的性能功耗比

如圖7,其中的TPU’是使用了GDDR5存儲的改進型。可以看到,相比CPU性能提升196倍,相比GPU性能提升68倍。谷歌隨后又開發了TPU 2.0、3.0版本。TPU 1.0的性能峰值達到了92Tops,而TPU2.0性能峰值達到180Tflops,TPU3.0更是達到了420Tflops。并且,從TPU 2.0開始,TPU不再是作為一個加速卡應用于通用服務器,而是定制的TPU集群,這樣會更大限度的發揮TPU的加速價值。

3.3 網絡領域DSA案例:Intel Tofino

SDN蓬勃發展,從控制面可編程的Openflow到數據面可編程的P4語言,以及出現了Intel PISA架構的Tofino芯片。站在體系結構的視角,Tofino是網絡領域最典型的DSA,其實現的可編程流水線既能夠達到ASIC級別的性能,又能夠通過P4對整個包處理數據面進行編程。

Intel基于PISA架構,設計了面向數據中心的、支持P4數據面編程的ASIC交換芯片。其目標是使對網絡的編程與和CPU編程一樣簡單。當網絡是完全可編程的(即控制平面和數據平面都在最終用戶的控制之下)時,網絡行業將享有與軟件一樣飛速的發展。

在Intel看來,雖然已經存在NPU和FPGA,可以修改網絡協議和編輯數據包,并為那些知道如何編寫微代碼或RTL的人員提供適度的可編程性,但是它們跟ASIC的性能不在一個數量級。因此,NPU和FPGA只能在性能不敏感的地方找到用武之地。Intel為網絡行業提供兩全其美的解決方案:可編程性數據平面協議,并且達到行業最高速度。Intel不僅開發了全球第一個比傳統ASIC還要更快的可編程交換機芯片,而且還使得網絡編程變得容易并且通用。

Intel與Google、Microsoft、Princeton及Stanford合作,開發了用于編程網絡的開源網絡編程語言P4。程序員可以基于P4編程一次來描述網絡行為,然后編譯程序以在各種不同的平臺上運行。P4為網絡設備制造商和網絡所有者提供了差異化的手段,可以使產品或整個網絡比競爭對手更好。

這與當前的情況形成了鮮明對比,如果用戶想向網絡添加新功能,則必須與芯片供應商共享該功能,并看到它也出現在競爭對手的網絡中,從而打敗了差異化的目的。設備制造商也不愿意添加新功能。添加新功能需要花費幾年的時間,然后競爭優勢卻很短暫。這導致一些公司傾向于開發特有的固定功能ASIC,以保持領先地位。

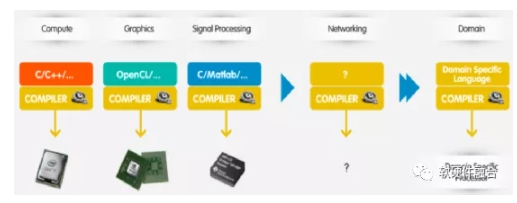

圖8. 像CPU編譯器一樣的網絡編譯器

如圖8所示,可編程性長期存在于計算、圖形、數字信號處理以及特定領域處理器中,從而使蓬勃發展的開發人員社區能夠快速創新并編寫以最終用戶為中心的解決方案。Intel的PISA架構可以像DSP、GPU以及TPU那樣,它將完全控制權交給網絡所有者。

為此,Intel首先確定了一個小規模的原語指令集來處理數據包,總共約11條指令。以及非常統一的可編程流水線(PISA架構),來快速連續地處理數據包頭。程序使用領域特定語言P4編寫,然后由Intel Capilano編譯器進行編譯,并經過優化以在PISA架構的設備上全線速運行。Intel的目標是使網絡更加敏捷、靈活、模塊化且成本更低。

Intel認為,網絡系統正朝著由三層構成的方向發展:在底部是一個P4可編程的Tofino交換機,在上面是一個基于Linux的操作系統,運行專有的控制平面應用程序。Intel為整個行業提供最快的、最高可編程性、經過P4優化的交換機硬件。

四、第四代:CASH超異構

4.1 芯片從2D到3D到4D,單個芯片所能容納的晶體管數量越來越多

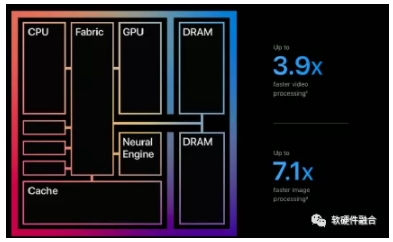

圖9. 蘋果公司M1芯片說明

如圖9所示,蘋果公司自研的ARM CPU M1基于TSMC 5nm工藝,具有160億個晶體管,如此巨大規模的設計,使得M1集成了8核CPU和8核GPU,并且每個處理器都可以非常奢侈的使用內部Register、Buffer或Cache資源(這些是晶體管消耗大戶)。

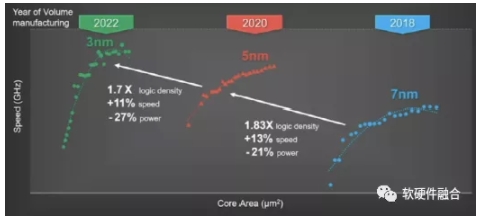

圖10. TSMC 新工藝Roadmap

如圖10所示,TSMC 5nm剛剛量產,其3nm工藝已經在路上,2nm、1nm也都在未來幾年的路線圖中。并且,TSMC已經開始在攻關0.1nm工藝,半導體工藝即將進入亞納米(埃米)時代。

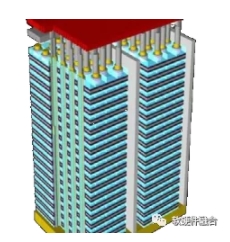

圖11. 3D存儲封裝

如圖11,在存儲領域,近些年來還興起了3D封裝技術,使得集成電路從二維進入三維。

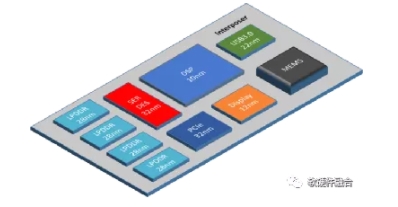

圖12. Chiplet示意圖

如圖12,芯粒(chiplet)機制,把多個芯片裸DIE集成到一起,從3D到4D,都進一步增強了單位面積的晶體管集成度。

工藝持續進步、3D堆疊以及Chiplet多Die互聯,使得芯片從2D->3D->4D。這些技術的進步,意味著在芯片這個尺度,可以容納更多的晶體管,也意味著芯片的規模越來越大。

4.2 從異構到超異構,從SOC到Multi-SOC,設計規模越來越龐大

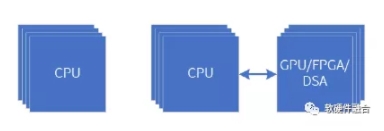

(a) CPU同構并行 (b) CPU + xPU異構并行

圖13. 同構并行和異構并行計算架構

當前,并行計算的主流架構如圖13所示:

- 圖13(a)為CPU同構并行。常見的多核CPU和多CPU socket互聯即是同構并行計算。CPU由于其靈活通用性好,是最常見的并行計算架構。但由于單個CPU核的性能已經到達瓶頸,并且單顆芯片所能容納的CPU核數也逐漸到頭。CPU同構并行已經沒有多少性能挖潛的空間。

- 圖13(b)為CPU+xPU的異構加速并行架構。一般情況下,GPU、FPGA及DSA加速器都是作為CPU的協處理加速器的形態存在,不是圖靈完備的。因此,這些加速器都需要CPU的控制,CPU+xPU成為了典型架構。

異構并行計算架構的情況說明:

- 如果CPU不參與計算,這時負責GPU等加速器的控制和任務和數據協同,則不需要性能特別強大的CPU。整個異構計算的計算性能基本由加速器決定。

- GPU作為加速器。GPU具有一定的靈活性,但效率相比DSA仍有差距,并且在可見的未來也會很快面臨和CPU一樣的性能瓶頸問題。

- FPGA作為加速器,受限于其編程難度和設計規模約束,通常作為FaaS平臺,充分利用FPGA硬件可編程的彈性。

- DSA作為加速器。DSA在極致性能的情況下,提供了一些靈活性。但面對的領域(Domain)應用多種多樣并且快速變化,一直沒能實現DSA芯片的大規模落地。

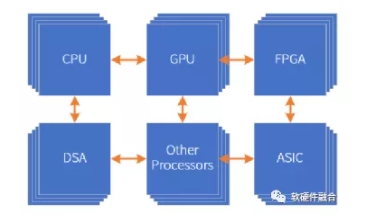

圖14. 多種處理引擎共存的超異構并行計算

隨著芯片工藝所能支撐的設計規模越來越大,并且,CPU、GPU、FPGA、一些特定的算法引擎,都可以作為IP,被集成到更大的系統中。這樣,構建一個更大規模的芯片設計成為了可能。在這里,我們提出“超異構”并行計算的概念,如圖14,超異構指的是由CPU、GPU、FPGA、DSA、ASIC以及其他各種形態的處理器引擎共同組成的復雜芯片系統。

站在系統的角度,傳統的SOC是單系統,而超異構系統則是多個系統整合到一個更加龐大的宏系統。傳統SOC和超異構SOC的區別和聯系:

- 設計規模的不同。MCU芯片是SOC,手機芯片是SOC,超異構架構芯片也是SOC。那么區別在哪里呢?但MCU級別SOC通常不跑操作系統或者跑RTOS級別的操作系統,進行一些簡單的控制和處理。而手機SOC則需要運行大型操作系統,如安卓、IOS等,使得我們的手機越來越接近于一臺電腦。而超異構架構,則不簡單是運行操作系統和各種軟件,而是聚焦提供既性能強勁并且軟件能夠靈活充分使用的龐大資源池;在底層軟件的協助下,把硬件變成一個無差別的計算平臺資源池,供軟件隨意的切分組合,把算力更靈活的提供給用戶。

- 單系統和多系統。傳統的SOC,更多的是有一個基于CPU的核心控制程序,來驅動CPU、GPU、外圍其他模塊以及接口數據IO等的工作。可以說,整個系統的運行是集中式管理和控制的。而超異構由于其規模和復雜度,則很難做到這一點,每個子系統其實就是一個傳統SOC級別的系統,然后這些系統需要根據一些特定的協議進行交互。整個超異構的系統呈現出分布式系統的特點。

- 數據流驅動還是指令流驅動。傳統SOC中,CPU是由指令流(程序)來驅動運行的,然后CPU作為一切的“主管”再驅動外圍的GPU、其他加速模塊、IO模塊運行。而在超異構的多SOC系統中,由于系統復雜度的影響,指令流的設計模式很難“同步”不同系統間的控制交互。整個交互實際上是由數據交互產生的。并且,由于要處理的數據帶寬的急劇增大,很多處理引擎都是數據流驅動的模式,而不是指令流驅動。表現在整個宏系統上,都可以理解為數據流在驅動整個系統運轉。

超異構需要實現相比傳統基于GPU或DSA的異構計算10倍甚至100倍以上的性能提升,并且需要實現整體接近于ASIC的極致的性能,還要確保整個系統的接近于CPU軟件的通用可編程能力。

4.3 軟硬件融合,超異構計算的必由之路

由于云計算的發展,數據中心已經發展到超大規模,每個超大規模數據中心擁有數以萬計甚至十萬計的服務器規模。超大規模數據中心的發展,是云計算逐漸走向軟硬件融合的根本性驅動力量。

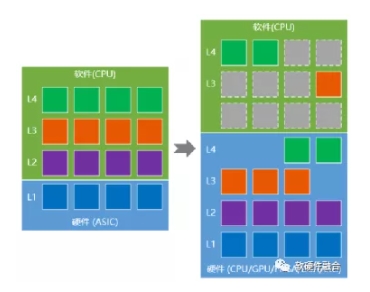

圖15. 軟硬件融合和CPU系統不斷卸載

云服務器上運行的各類軟件可以看做是一個非常復雜的并且分層的系統, 由于CPU已經性能瓶頸,在宏觀的數據中心規模的加持下, 以及IaaS層針對特定場景優化的一些服務,如圖15所示,我們可以認為:軟硬件融合的過程其實就是系統不斷卸載的過程。

軟硬件融合:

- 不改變系統層次結構和組件交互關系,但打破軟硬件的界限,通過系統級的協同設計,達成整體最優。

- 傳統分層很清晰,下層硬件上層軟件;軟硬件融合的分層分塊,每個任務模塊是軟件還是硬件,或軟硬件協同,都有可能。軟件中有硬件,硬件中有軟件,軟硬件融合成一體。

- 宏觀的看,越上層越靈活軟件成分越多,越下層越固定硬件成分越多。龐大的規模以及特定場景服務,使得云計算底層Workload逐漸穩定并且逐步Offload到硬件(被動趨勢)。

- 軟硬件融合架構,使得“硬件”更加靈活,功能也更加強大,這樣使得更多的層次功能向“硬件”加速轉移(主動搶占)。

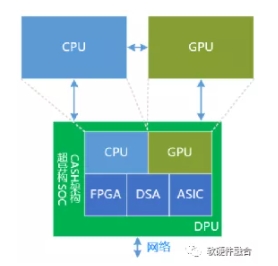

圖16. 基于CASH架構超異構實現的DPU

通常,我們把DPU當做是CPU的任務卸載加速,這個想法依然沒有擺脫以CPU為中心架構設計的“桎梏”。

更本質的,如圖16所示,基于CASH架構(CASH,Converged Architecture of Software and Hardware,軟硬件融合架構)的DPU,是一個性能強勁的、功能完整的、超異構計算的算力平臺。在這個平臺里,包含了硬件加速部分去完成底層基礎設施層的加速處理;也包含了,用于應用層處理的CPU和GPU,來完成應用層的處理。

獨立的CPU和GPU可以看做是DPU的擴展,只有當集成的CPU/GPU不滿足處理要求時,作為獨立的計算平臺,來增強整個系統的功能。

圖17. 軟硬件融合技術是各種復雜計算場景的基礎支撐

軟硬件融合技術,是為了應對算力需求最高、系統規模最大、成本最敏感、靈活性要求最高的云計算數據中心場景的各種復雜挑戰,而逐漸形成的技術理念和一整套技術體系。

基于軟硬件融合的超異構混合計算,聚焦算力需求再上1-2個數量級的復雜場景。面向未來,自動駕駛、5G/6G核心網、邊緣計算等場景,對算力的需求都會更加強勁,面對如此多的復雜系統場景,軟硬件融合也有了更多的用武之地。

如圖17,軟硬件融合從云計算抽象出來,反過來指引包括云計算、自動駕駛等復雜系統場景的芯片及系統設計。

總結:

軟硬件融合的超異構計算需要達到如下一些標準:

性能。單位晶體管資源的性能水平接近于ASIC,整體性能需要達到GPGPU、DSA的10-100倍甚至以上。

通用靈活性。在保證性能極致的基礎上,要確保其可編程能力達到接近于CPU軟件的水平。并且給開發者提供友好的編程平臺。

開放、開源。CPU有x86、ARM和RISC-v三大主流的架構平臺,而DSA方面,完全是各家自己定義的各種互不兼容的架構。到了超異構時代,在軟件定義的加持下,一定需要開放的標準化的架構定義,才能真正實現不同架構不同軟件生態之間的“互聯互通”。

各個平臺的算力和通用性總結如下圖18所示。

圖18. CPU、GPU、DSA、CASH算力平臺比較