FPGA+CPU架構的自動駕駛平臺性能分析

1 介紹

由于在自動駕駛領域需要對傳感器的數據作大量的基于深度內神經網絡的復雜運算,GPU和FPGA被不約而同地用來作為對CPU的一種加速器被使用。這樣做不僅可以提高計算性能,并且可以大幅度地降低能耗。FPGA+CPU架構的自動駕駛平臺憑借其靈活性,高效率,低能耗等特點,正越來越多地被一大批擁有技術實力的公司使用,比如Waymo,百度,福特,通用等。在這里本文試圖探討如何對FPGA+CPU自動駕駛平臺的性能進行估計,目的是希望幫助開發者在選擇FPGA+CPU自動駕駛系統平臺時初步掌握一種對系統性能的評估方法。本文將以Xilinx 推出的Zynq UltraScale+ MPSoC ( Part#=ZU19EG )為例,來闡述其方法。

由于作者知識水平和寫作方法的局限,如讀者能指出錯誤紕漏之處,將萬分感謝。

2 基于FPGA+CPU的自動駕駛平臺系統設計

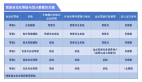

圖一 是比較典型的基于FPGA+CPU的自動駕駛系統原理圖。一般來說配置一個多核的應用處理器單元-Application Processor Unit(簡稱AP)用來跑一個或者多個操作系統,主要用來任務調度,管理等工作,而大數據的處理:比如圖像的特征值提取,目標類別識別,多目標跟蹤,運動預測等復雜運算多放在FPGA 的可編程邏輯模組Programmable Logic(簡稱PL)來處理。衡量自動駕駛平臺的性能,關鍵點在幾方面:1、系統對大數據的處理能力,在這里就是要了解FPGA的PL模組的運算能力。2、復雜多任務的處理能力,即應用處理器CPU的運算能力。3、高速海量數據的傳遞,即傳感器的數據接收,以及PL和AP之間的數據通訊能力。

由于篇幅原因,本文將只對第1點進行詳細敘述,而第2,3點只做簡單敘述。

圖一:基于FPGA+CPU的自動駕駛平臺原理圖

3 如何計算FPGA PL的性能

3.1 FPGA 性能難以計算

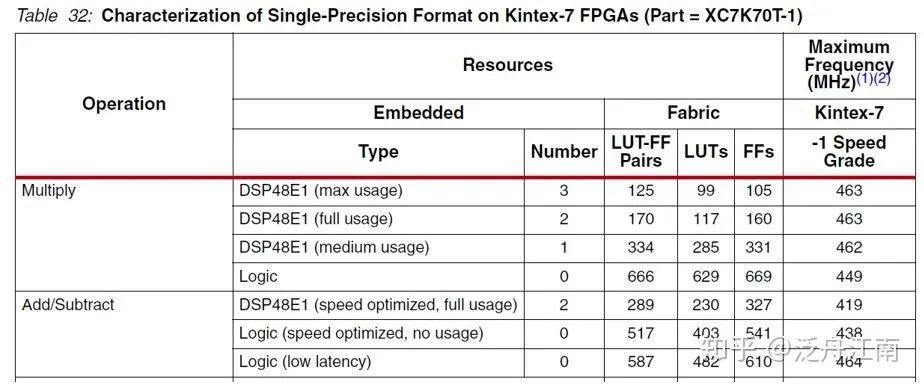

在介紹如何計算FPGA的性能之前,我們來了解一下目前主流的FPGA的硬件。以Xilinx的Zynq UltraScale+ MPSoC為例,其PL包含可編程資源 Logic blocks, RAM, DSP slices等。而要得到最終的FPGA 性能值,由于以下幾點原因而變得困難。

- 不太容易知道需要多少個logic cell和DSP slice才能構造成一個加法器。這個數量是FPGA IP core供應商決定的,用戶難以知曉

- 通常FPGA用來實現和Application processor通訊的I/O設備需要占用一定數量的Logic cell,導致FPGA 資源不可能全部被利用到構造加法器

- 浮點運算會導致設計的clock無法達到100%的設計指標,相對于設計的clock頻率指標,只能達到在80%左右

- 溫度影響也要求系統的clock必須作出調整而不能以一個固定的值來計算

3.2 一種PFGA性能計算方法

目前通常使用的方法是參考系統的每秒浮點運算操作(floating-point operations per second ),簡稱FLOPS。因為浮點運算用到的所有的高階函數,比如除法,平方,三角函數等,都能歸結為加法,乘法運算,且常用的傅里葉變換,矩陣操作也都可以用加法器(adder)和乘法器(multipliers)的組合來實現,所以FLOPS和加法器/乘法器的數量在衡量其運算性能上是直接關聯的。

為了計算FPGA的最大運算能力,我們可以通過利用單精度(Single-Precision)數據加法器數量的方法來求出一個系統的FLOPS。較乘法器而言,加法器利用到的系統資源少,求出的系統FLOPS的值就會接近最大值。

假設所有的運算都是并行的,那么可以得到下面的FLOPS計算公式:FPGA PL FLOPS = ( Clock1 x LC based Adder#) + ( Clock2 x DSP48 based Adder#)根據以上公式,下面我們以Xilinx的Zynq UltraScale+ MPSoC的ZU19EG為例,來求其FLOPS。

3.3 FPGA的總資源

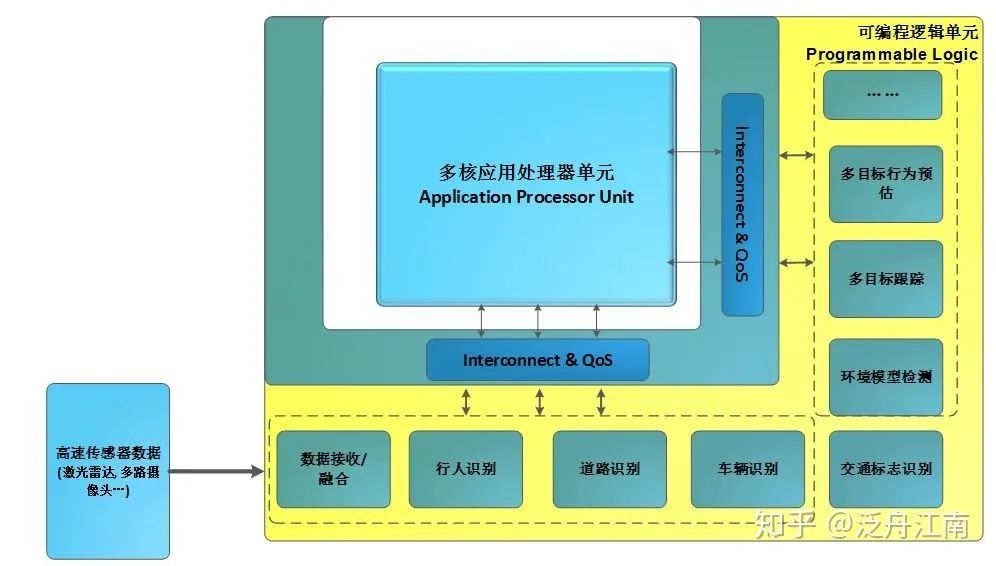

由圖二,Zynq UltraScale+ (Part=ZU19EG) 擁有的資源列表,我們可以看到它有1,143,450個Logic cell, 1,968個DSP slices。

圖二:Xilinx Zynq UltraScale+資源列表

圖二:Xilinx Zynq UltraScale+資源列表

3.4 PL加法器數量的計算

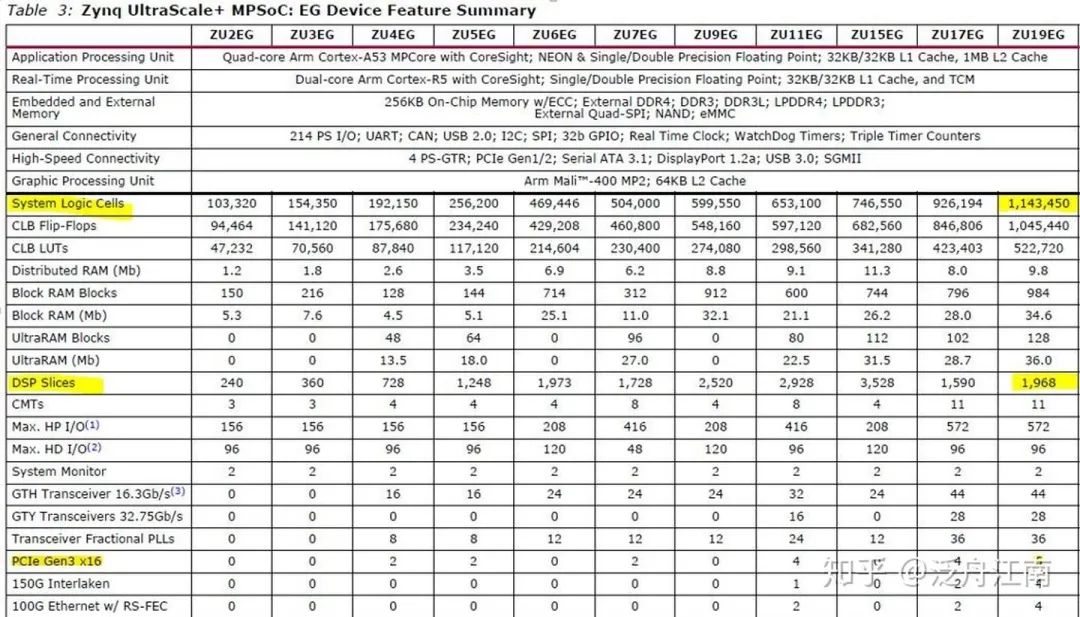

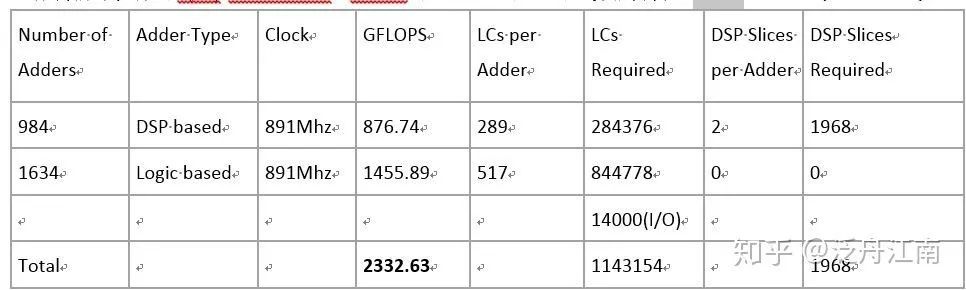

IP Core的實現方式由算法供應商決定,在這里僅以Xilinx提供的基于Kintex-7上的加法器IP Core用到的資源作為參考,誤差應該在可接受范圍。如圖三,可以得知:

- 1個基于DSP48E 的加法器需要2個DSP slices和289LUT-FF pairs組成

- 1個基于Logic cell 的加法器需要517 Logic Cells組成

圖三 支持單精度的FPGA特征由于實現相關的I/O設備,必須占用掉一定數量的Logic Cell,這里我們假設用掉14000個Logic Cell. 也即:Logic Cell 剩下總數 = 1143450 - 14000 = 1129450由于要計算出最大值,我們需要假設盡可能多的使用所有資源,這樣可以得出:

- DSP48 based adder amount = 1968 / 2 = 984 (個)

- LC based Adder amount = (1129450 - 984*289) / 517 = 1634(個)

3.5 加法器的Clock

我們可以得知:

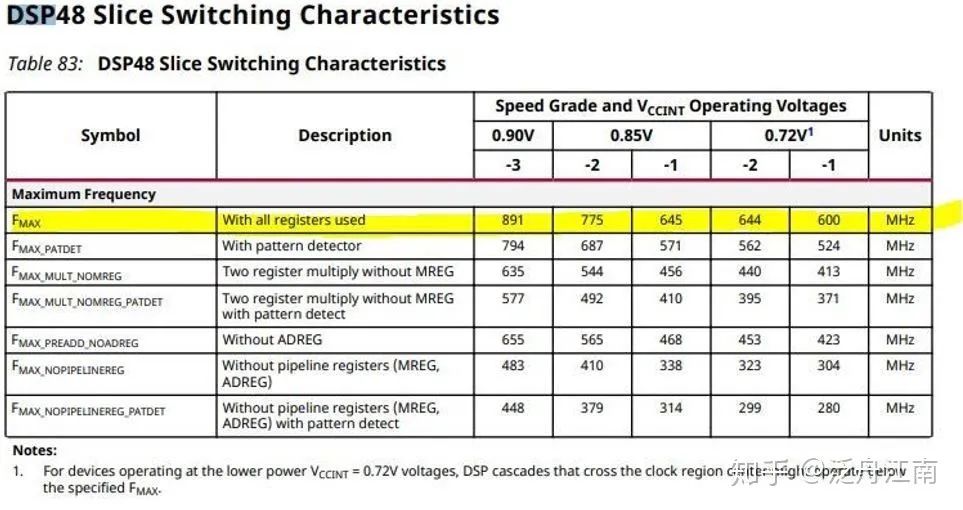

- 基于DSP48 的加法器的clock范圍在:600 Mhz(slow) - 891Mhz (fastest)

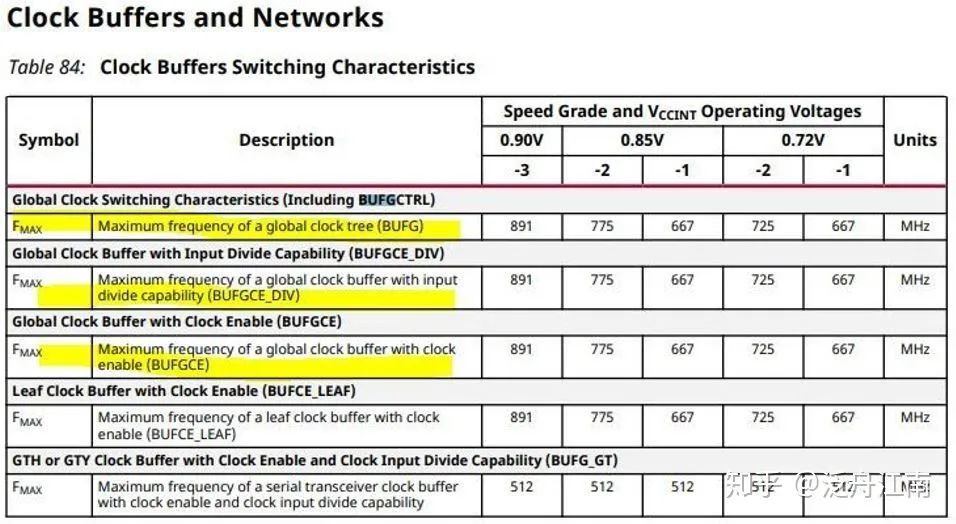

- 基于Logic cell的加法器的clock范圍在:667 Mhz(slow) - 891Mhz (fastest)

圖四 DSP slice 頻率參數特征

圖四 DSP slice 頻率參數特征

圖五 Global 時鐘參數特征根據不同的溫度條件,Fmax的值需要相應調整。比如:

- 當溫度條件在0-100度時,給加法器設置的clock可以設置較高為891Mhz

- 當溫度條件在-40-100度時,給加法器設置的clock需要調整為600Mhz/667Mhz

為了計算最大運算能力,我們采用在0-100度的條件下的clock值,也就是891MHz。

圖六 各個模組算力一覽這樣我們可以得出Zynq UltraScale+ MPSoC的ZU19EG的PL的運算能力為:2332 GFLPOS (~2 TFLOPS)總結: ~2T FLOPS某種程度上反映了FPGA Zynq UltraScale+ ZU19EG PL的處理能力。如果針對汽車級別產品而言,-40度至100度溫度的限制,整體PL的 FLOPS值應該在1 FLPOS - 1.5T FLPOS之間比較恰當。

4 如何計算FPGA AP的性能

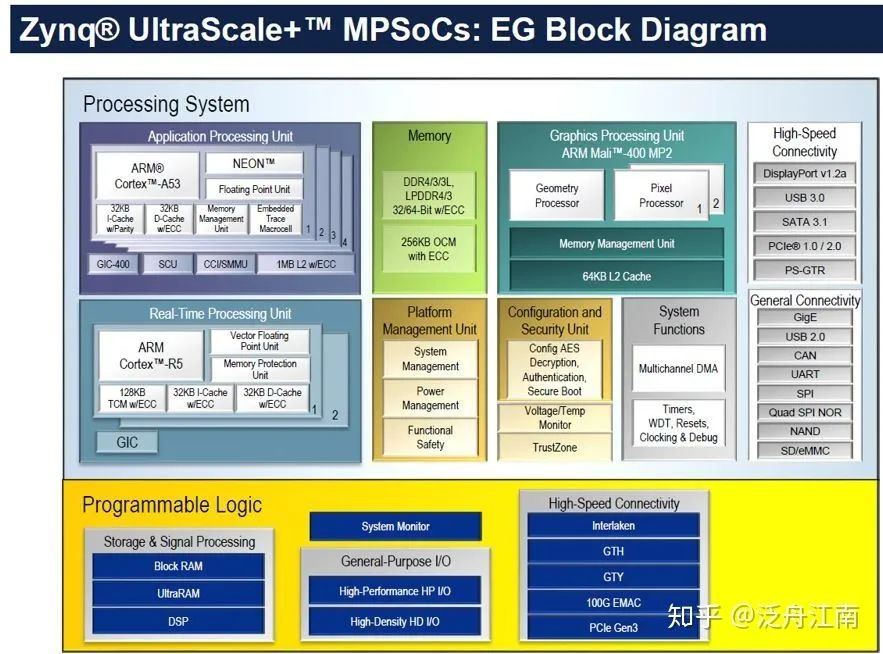

如圖七,Xilinx的MPSoc+FPGA系列產品則完全可以叫SoC了,其不僅包含多個ARM CPU內核,還有針對安全領域的R5內核,還有Mali 400這樣的GPU。從下面的圖,可以得知FPGA Zynq UltraScale+ ZU19EG擁有

- CPU#1:Quad-coreARM? Cortex?-A53 MPCore? up to 1.5GHz

- CPU#2:Dual-coreARM Cortex-R5 MPCore? up to 600MHz

- GPU:Mali?-400 MP2 up to 667MHz

圖七 Xilinx FPGA Zynq UltraScale+ ZU19EG框圖估算下來:

- CPU#1 & CPU2 總運算能力:2.24 x 1.5 x 1000 x 4 + 2.0 x 600 x2 ~= 15840 DMIPS

- GPU運算能力:2 GFLPOS

Note: Cortex-R5 : 1.67 / 2.02 / 2.45 DMIPS/MHzCorte-A53: 2.24 DMIPS/MHz

5 FPGA 架構的靈活性

目前通用的認知是Level3的自動駕駛需要系統擁有~350,000DMIPS的運算能力,才可能實現比如雷達/視頻的處理,主動避讓,自動泊車等。以上章節所說的MPSoc+FPGA已經有足夠的計算能力足以支持Level3左右的自動駕駛在一般場景下的運用。

然而為了支持更多的自動駕駛Level4/Level5的場景,由于FPGA的接口靈活性,很容易在和FPGA的基礎上額外增加子計算模塊,整個系統運算能力將突飛猛進,這樣極大地方便了平衡運算力到不同的運算單元。比如:可以把激光雷達的數據處理單獨放到某一個Intel Xeon 子計算模塊執行,FPGA母板只需要控制邏輯,把激光雷達數據通過高速接口(PCIe或者10G以太網)傳遞給子計算模塊讓其進行大量的數據處理。

FPGA的靈活性可以讓開發者拓展出越來越多的可能。