【工程師筆記】第七期:Xeon Phi要自我互連,CPU靠邊站

做技術的朋友可能有過類似這樣的感覺——每天都會遇到新的問題,或者學到新的知識。然而一個人的時間和精力畢竟有限,不是所有的崗位都能做到總是親力親為,每人最擅長的領域也各不相同。為了使工程師自己踩過的坑、那些實用的心得體會也能給大家帶來幫助,把經驗記錄和分享出來就顯得尤為可貴,這就是我們開設《工程師筆記》專欄的目的。

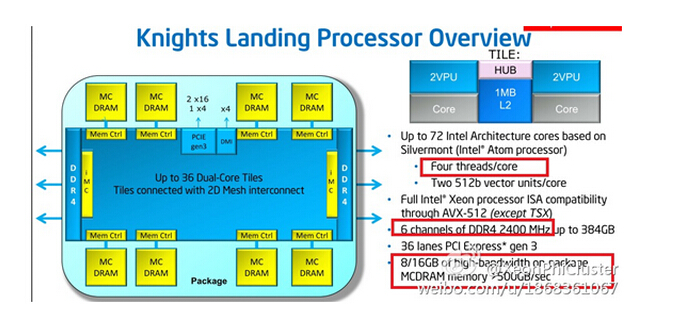

在《從260核異構申威看HPC Top500縮影》一文中,我給大家介紹過在最新的超算榜單上為國爭光的“神威太湖之光”。而在同一次大會上,Intel也正式發布了代號為Knights Landing的新一代Xeon Phi Processor x200(注意:不再是coprocessor/協處理器了)。

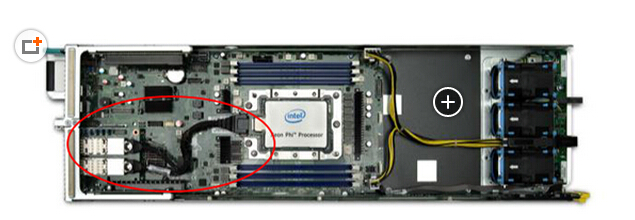

這個照片應該是Intel的參考平臺,尺寸上大致符合2U 4節點的密度,在Xeon Phi Processor兩側有6個DDR4內存插槽。用紅圈標出的部分應該就是將Omni-Path網絡引出機箱的連接器件。

至本文截稿之時,官網上我還沒找到關于Xeon Phi x200的詳細資料,不過早在去年底翻譯自國外的新聞中已經有過不錯的介紹。

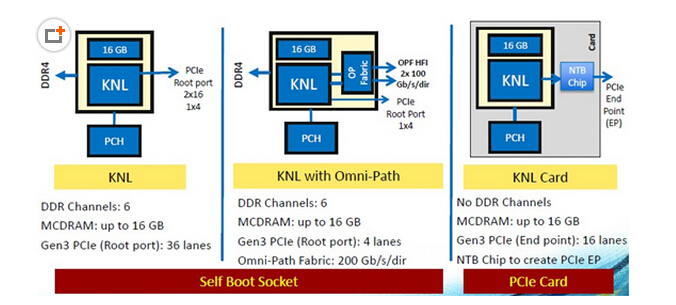

如上圖,“Self Boot Socket”的Knights Landing除了DDR4內存控制器之外,還可以提供36個PCIe Gen3 lane,感覺是移植了Xeon CPU的uncore部分設計。不過,提供2個Omni-Path 100Gb/s網口的型號就少了2個PCIe x16,讓我覺得這一代產品的片上OPA互連控制器走的還是PCIe?最右邊的PCIe插卡形態,去掉了DDR內存通道,能不能不要那個PCH南橋呢?

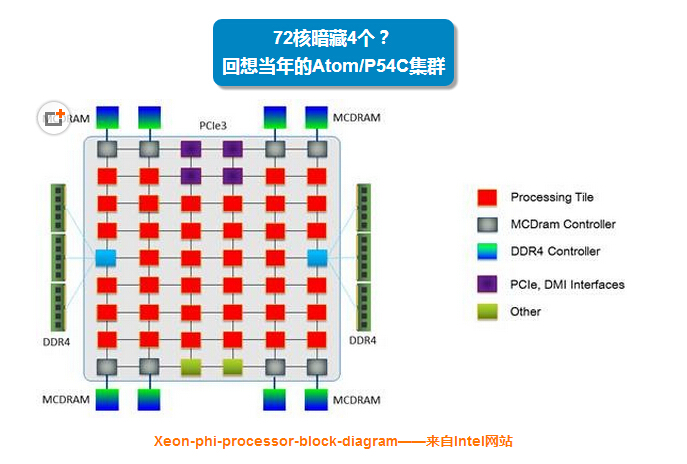

上下兩張圖可以結合起來看。我數了一下紅色Processing Tile的數量是38個,如此則該架構設計應該支持最多76個核心,目前限制在72個可能是為了保證良品率,或者功耗考慮?

根據右邊的解釋,每個“tile”中有2個Core共享1MB L2 Cache,每個Core支持4線程并包含2個AVX-512矢量單元(浮點計算應該就是靠它來進行的)。Intel還提到了這些Core是基于Atom處理器內核,記得之前還有一種說法是P54C。P54C即當年Intel Pentium 75-166的核心代號,1997年我自己的第一臺電腦用的就是奔騰133。

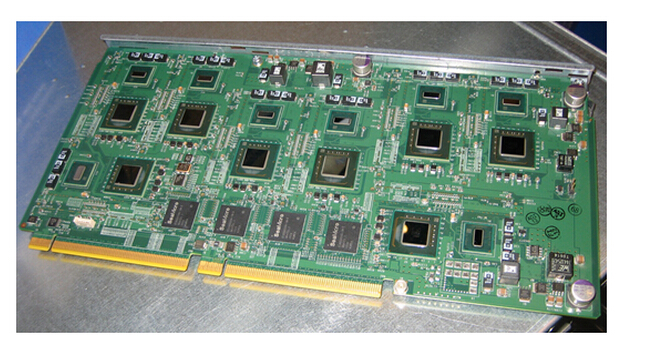

在2011年春季北京IDF上,我曾經看到這套由微服務器廠商SeaMicro打造的高密度系統,展板上介紹在10U機箱內容納了256個雙核Atom,當時負責展臺的朋友也提到了P54C。不知大家有沒有覺得神威太湖之光的節點布局有點像這個?

我猜測這個系統很早就開始用于預研今天的Xeon Phi Processor,當然此時它還談不上芯片集成度和成本效益。從照片中看每顆Atom旁邊應該都有一顆南橋(當時還不是SoC),內存等可能在PCB背面,4顆印著SeaMicro的芯片估計是用于互連。

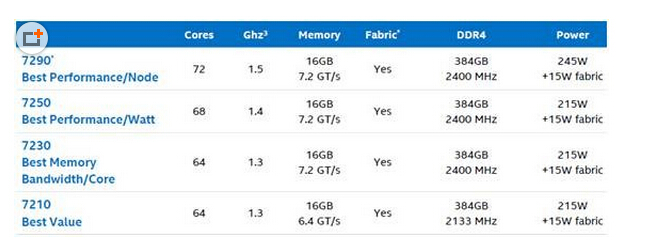

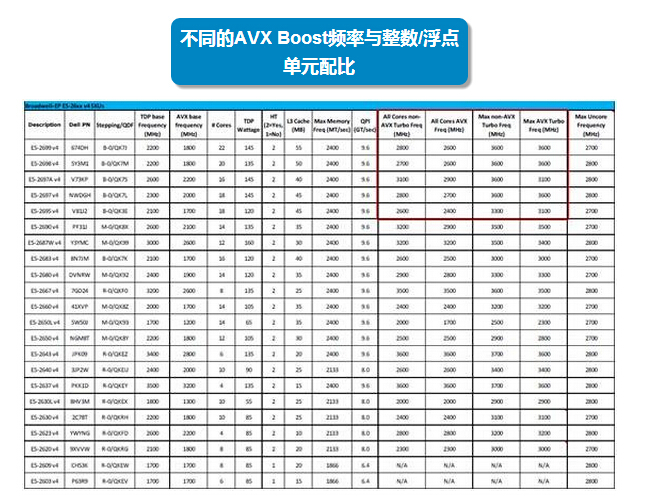

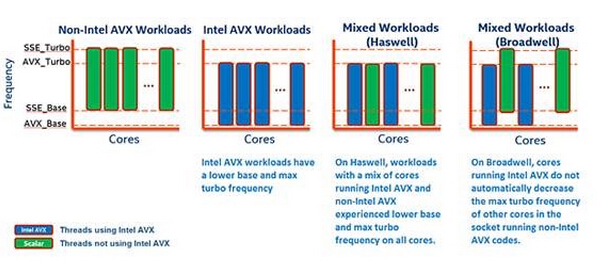

撰寫上一篇《工程師筆記:一項Xeon E5-2600 v4測試數據的背后》的過程中,在Dell的Solutions Performance Analysis文檔中我看到了以上規格表,其中有non-AVX和AVX單元不同的TurboBoost超頻頻率。讓我們放大來看一下:

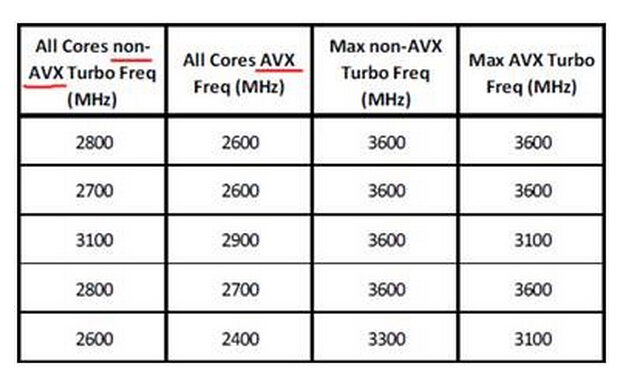

對于所有核心一起工作時的TurboBoost,non-AVX的頻率比AVX要高,而最大(少數核心工作)TurboBoost頻率有些型號的CPU也存在差別。

上圖來自Intel資料,描述了Xeon E5v4(Broadwell)的一點改進。在此之前如果AVX和non-AVX負載在不同Core上混合運行,只能統一跑在兩者中較低的TurboBoost頻率上。而在Xeon E5v4上,則運行AVX的Core頻率不會降低到其它Core的TurboBoost水平。

我有個理解不知是否準確:由于用途的原因,整數/浮點單元的設計偏重與配比是Xeon Phi Processor與Xeon CPU的重要區別。至于Intel為什么沒有進一步像申威26010那樣“將MPE(管理單元)減少到4個來搭配256個CPE(計算單元)”?我覺得是考慮到通用性,畢竟Xeon Phi仍屬于x86指令集的一個擴展。

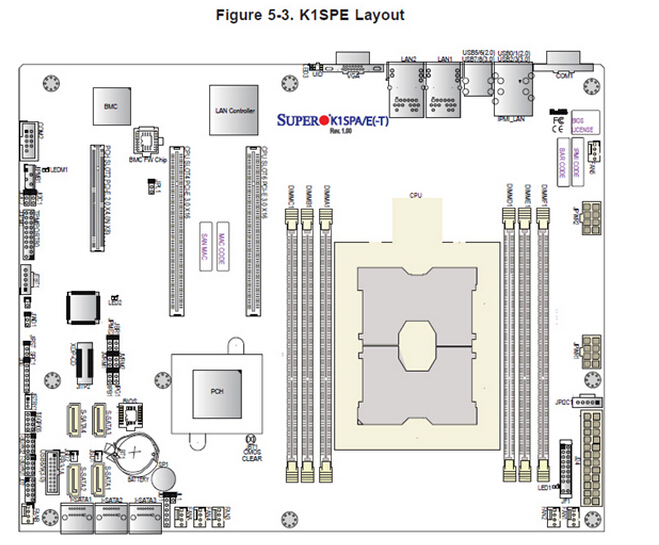

目前正式發布支持Xeon Phi Processor x200服務器產品的公司還不多,其中包括SuperMicro的主板和準系統(就是加個塔式機箱),或許只是先出個通用平臺還沒有太多特點。

SuperMicro K1SPA/E (-T) 主板示意圖,可以看到“巨大”的LGA-3647 CPU插座,據了解下一代Xeon E5可能也會用這個Socket。

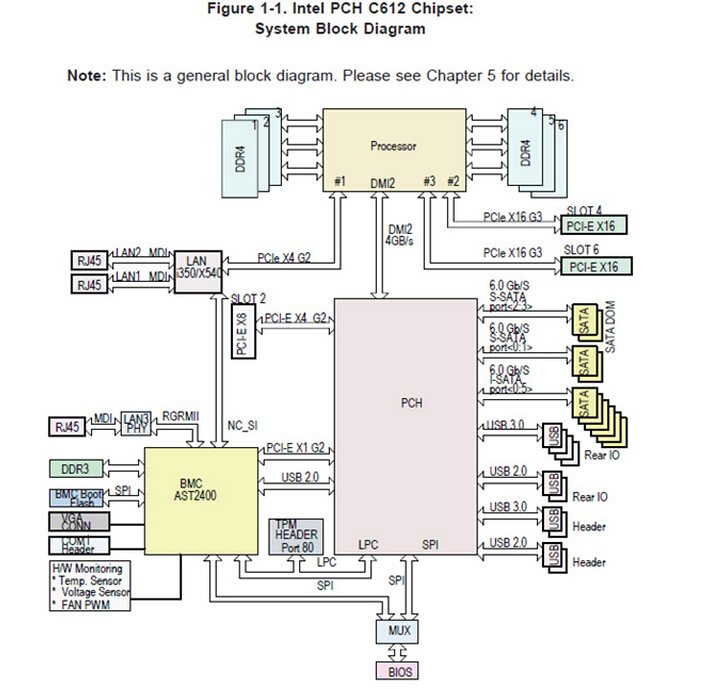

上面是SuperMicro這款主板的結構圖。涉及PCH 612的部分與傳統Xeon服務器并沒有明顯的不同;除了內存通道之外,從處理器引出的PCIe x16 Gen3插槽也許不再支持拆分成x8或者x4,因為Xeon Phi的定位就是HPC,除了高速網絡互連應該啥也不缺了。

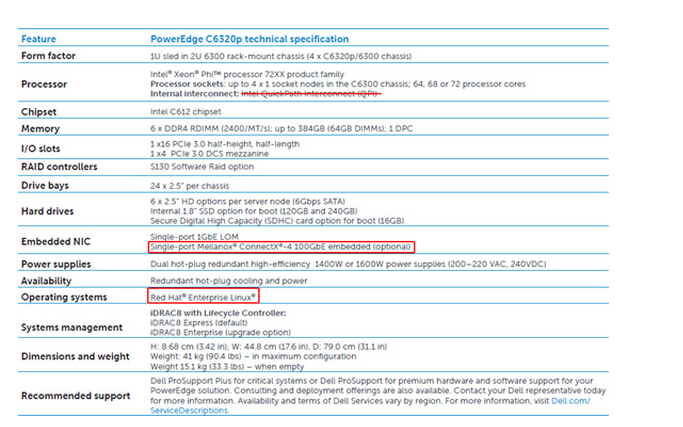

戴爾的這款PowerEdge C6320p,可以理解為是在2U 4節點機箱基礎上將C6320 Xeon E5計算節點換成了Xeon Phi Processor節點。它比較接近前面我們列出的Intel參考平臺,具備計算密度并適合大規模部署。

可能是由于初版資料,規格表中Xeon Phi Processor 72XX不支持的QPI還沒來得及修改徹底。C6320p有幾種硬盤/閃存支持選項,提供戴爾統一的iDRAC8服務器管理,聽說可以直接安裝Red Hat企業版Linux,具體注意事項有待后續確認。不過為了發揮AVX-512計算單元的能力,還是需要運行相應的編譯好的程序。

關于集成單端口Mellanox ConnectX-4 100GbE網卡這個可選項,為什么不是InfiniBand EDR呢?其實該公司近幾年對以太網的支持也不錯,可以在同樣的硬件上實現兩種網絡支持,比如EoIB這樣的方式。

上圖來自戴爾網站,可見這個100Gb網口應該是支持IB的。據了解PowerEdge C6320p也做好了支持Omni-Path的準備,除了現在可以使用Intel Omni-Path Host Fabric Adapter 100 Series PCIe網卡之外,等今年四季度Xeon Phi Processor 72xxF推出之后,像Intel參考平臺中那樣將Omni-Path引出機箱的連接器件也可以使用。

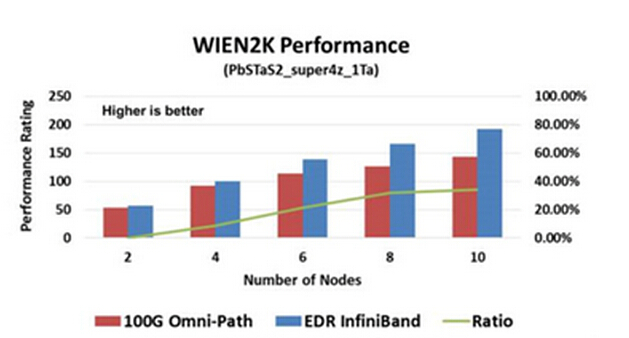

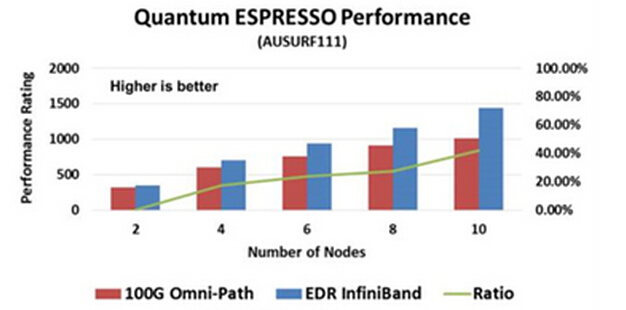

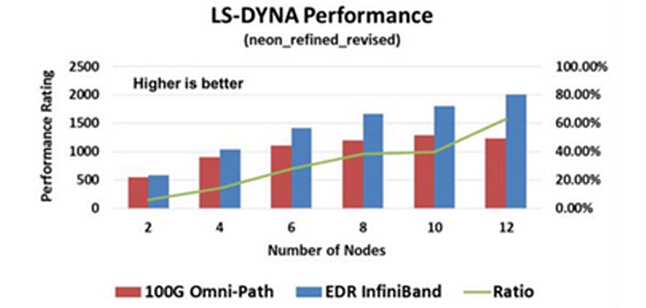

以上圖表僅供參考,因為在Intel的宣傳資料中您很可能會看到另外一些不同的測試數字。

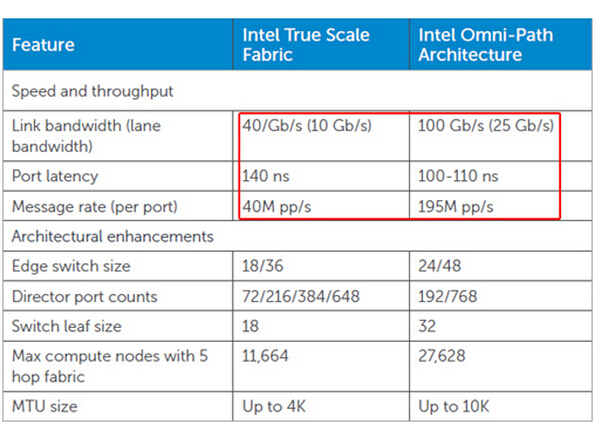

True Scale就是當初QLogic的40Gb/s InfiniBand產品線,可以看出100Gb/s的Intel Omni-Path在端口延時、發包速率上的優勢。既然是在IB技術上發展而來,Omni-Path可能需要一個成熟的過程,但我不認為有太大的困難。

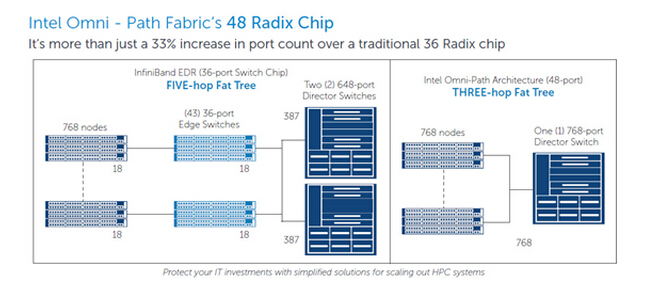

Intel還列出了交換機方面的一些優勢。比如Edge(邊緣)交換機48口比IB的36口多,服務器節點可以不通過邊緣交換機直連Director(導向器)等。

關于HPC網絡方面的最終戰局,我覺得要看Intel Omni-Path怎么個賣法。如果未來某一代CPU/Xeon Phi Processor無論你用不用全都集成的話……