Windows CE平臺下SDRAM的設計方案

SDRAM是指同步動態隨機存取存儲器,其從發展到現在主要經歷了四代,并廣泛的應用于各類操作系統上,隨著嵌入式產品的發展,各種嵌入式操作系統,以及嵌入式上層應用軟件層出不窮,這就對大容量SDRAM的需求日益增強。

目前用于嵌入式產品中的存儲器主要有FLASH和SDRAM。FLASH作為靜態存儲器,被應用于存放啟動代碼和操作系統內核,SDRAM作為動態存儲器,被應用于存放實時更新的數據信息。在此,采用Intel的PXA255處理器。使用32 MB的NOR FLASH作為放置啟動代碼和操作系統的靜態存儲空間,使用256 MB的SDRAM作為動態存儲空問,使用2 GB的CF卡作為應用程序和數據的存儲空間,并與液晶顯示屏、音頻、觸摸一起構成一個功能強大的嵌入式體系。

1 隨機存儲器介紹

隨機存儲器主要分為靜態隨機存儲器(SRAM)、動態隨機存儲器(DRAM)及SDRAM。1個SRAM單元通常由4~6個晶體管組成,當這個SRAM單元被賦予O或者1的狀態之后,它會保持這個狀態直到下次被賦予新的狀態或者斷電之后才會更改或者消失。SRAM的讀寫速度相對比較快,而且比較省電,但是存儲1 b的信息需要4~6只晶體管。DRAM和SDRAM必須在一定的時間內不停地刷新才能保持其中存儲的數據,但存儲1 b的信息只要1只晶體管就可以實現。在數據讀寫的過程中,SRAM,DRAM及SDRAM均有不同的工作方式。DRAM和SDRAM相對于SRAM增加了多路尋址技術,即利用2個連續的周期傳輸地址數據,達到使用一半的地址線,以完成SRAM同樣功能的目的。SDRAM相對于DRAM不僅提出了多Bank的工作模式,并且SDRAM與CPU和芯片組共享時鐘,芯片組可以主動地在每個時鐘的上升沿發給sDRAM控制命令。

2 硬件設計方案

2.1 SDRAM工作原理

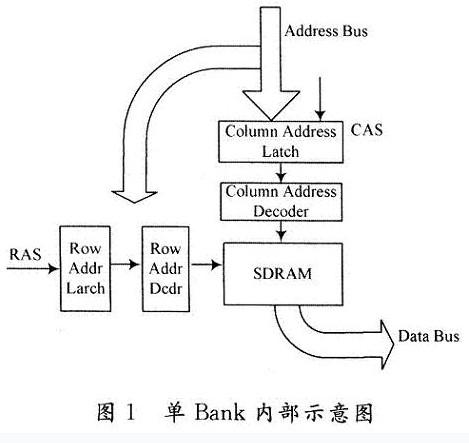

SDRAM本身是由多個Bank區域構成,對SDRAM的操作實際上是通過區域片選信號對單獨Bank進行的操作。SDRAM中單個Bank的讀取過程如圖1所示。

(1)通過地址總線將行地址傳輸到地址引腳;

(2)RAS(行地址使能信號)被激活,這樣行地址被傳送到行地址門閂線路中;

(3)行地址解碼器根據接收到的數據選擇相應的行;

(4)wE(寫使能信號)引腳確定不被激活,所以SDRAM知道它不會進行寫操作;

(5)列地址通過地址總線傳輸到地址引腳;

(6)CAS(列地址使能信號)引腳被激活,這樣地址被傳送到列地址門閂線路中;

(7)DQM(輸出使能)引腳被激活,數據向外輸出。

這就完成了一個單Bank的讀操作,在讀取數據的過程中行列地址的尋址過程是通過兩個時鐘周期實現的,在第一個時鐘周期使能行地址,下一個時鐘周期使能列地址,這就實現了地址線的復用,SDRAM寫入的過程和讀取過程是基本一樣的,只需要將wE信號激活。

2.2 硬件設計

對于SDRAM的硬件設計需要確定3個方面的內容:通過處理器的特性選擇SDRAM的型號;確定SDRAM地址線、數據線的連接方式;確定SDRAM控制信號線的連接方式。

2.2.1 SDRAM的選擇

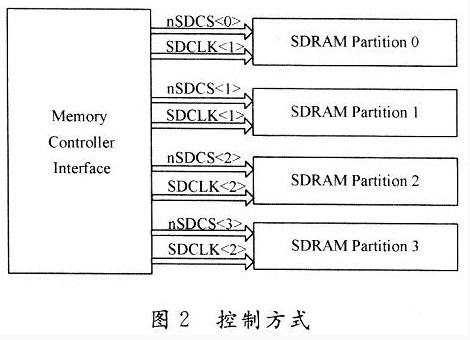

該平臺處理器選擇Intel公司XSCALE架構的PXA255,它針對于SDRAM有4根專用的動態片選信號,能夠支持4塊內存區域,如圖2所示。

其中每塊區域所能支持到的最大物理地址為64 MB。并且每一塊內存區域均可使用16 b或32 b的SDRAM。在硬件設計過程中考慮到硬件使用的可調節性,采用8片16 b×4 MB×4 Bank的SDRAM,共搭建了256 MB的極限存儲空間。其中,SDRAM選擇型號為三星公司的K4S561632E。

2.2.2 數據線、地址線的分配

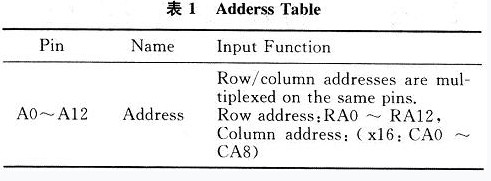

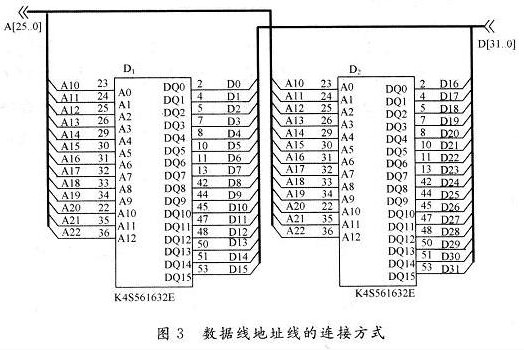

PXA255處理器共有32位數據線和26位地址線。故在硬件設計時需要并行處理2塊16 b的SDRAM,分別連接高位和低位的16根數據線,對于地址線的連接,首先需要參考SDRAM的數據手冊,確定SDRAM行列地址線的個數。其次根據處理器數據手冊確定具體地址線的連接方式。在三星K4S561632E的數據手冊中是這樣給出的,如表1所示。

從表1中可以得出行列復用13根地址線,其中行地址13根,列地址9根,共組成22根地址線的尋址空間。在處理器PXA255中,給SDRAM分配的地址線空間是從A10~A22。這樣就可以完全確定地址線和數據線的連接方式,如圖3所示。

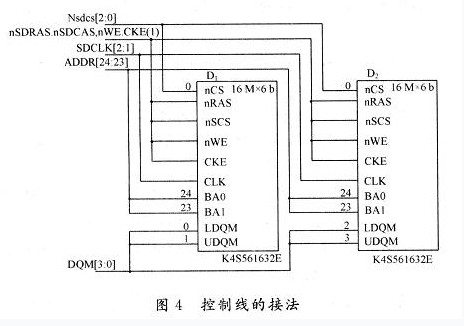

2.2.3 控制信號線的連接方式

對于SDRAM需要確定的控制線包括時鐘信號線、區域片選信號線及Bank片選信號線。對于這三類信號線PXA255處理器是這樣給出的,即:

(1)每兩組內存區域使用同一組時鐘信號線,即每128 MB的內存空間使用同一根時鐘信號線,故在設計中使用了2組時鐘信號線。

(2)共有4根區域片選信號,分別控制64 MB的物理地址空間。最大支持到256 MB的物理地址空間。

(3)地址線的23,24位用來實現對SDRAM內部Bank的選擇。

2.3 硬件的移植

針對于PXA27x系列的高端處理器,Intel并沒有對SDRAM部分做本質上的改動,仍然是4根動態片選信號,故硬件方面的設計可以完全移植到PXA27x系列的處理器中。 #p#

3 軟件設計方案

Windows CE操作系統下對內存的驅動代碼主要分為兩個部分,首先在BootLoader中對SDRAM進行底層初始化;其次在系統BSP包內需要將SDRAM所對應的物理地址映射為Windows CE下能夠識別的虛擬地址。

3.1 BootLoader代碼的買現

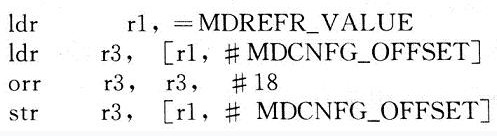

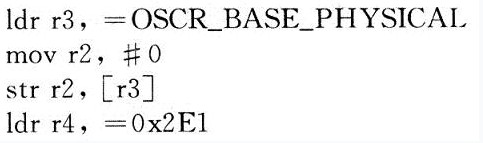

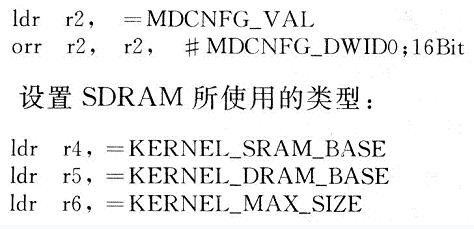

BootLoader是系統運行的起始點,它包含著系統運行的第一行代碼。BootLoader本身也是一個功能完整的微型操作系統,在內部需要實現任務調度、內存管理、文件系統,以及各種必要設備驅動程序的配置。其中內存管理即是完成SDRAM初始化的工作,包括設置SDRAM工作頻率、設置片選信號寄存器、設置刷新間隔和SDRAM潛伏期、以及配置系統內核的拷貝地址。控制線的連接方式如圖4所示。

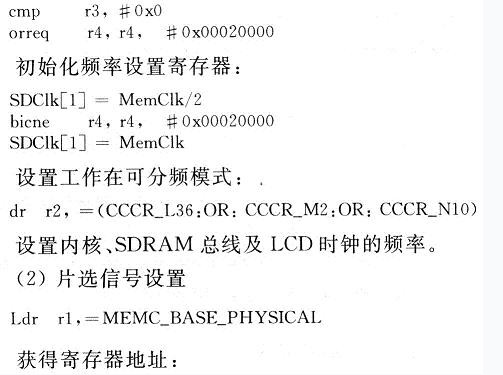

(1)頻率設置

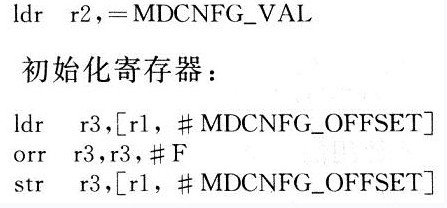

完成寄存器的復值,其中r3的選擇為F即就是0x1111,打開4片內存區域。

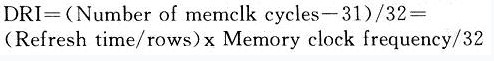

(2) 刷新間隔設置。關于刷新間隔值(DIR)的計算在手冊中是這樣給出的:

目前公認的標準是,存儲體中電容的數據有效保存期上限是64 ms,也就是說每一行刷新的循環周期是64 ms。這樣刷新速度為:64 ms/行數量。由于行地址有13位(在MDCNFG寄存器的DRACO[1:0]中設置,需要與硬件一致),所以每行的的刷新時間為64 ms/213=64 ms/8 192=7.812 5/μs,則7.812 5μs×100 MHz/32=0x18,這樣就得到了系統的DRI值。

(3) 潛伏期的設置。潛伏期是指SDRAM在讀寫過程中所存在的延遲,潛伏期的時間長度是由以下幾個參數共同決定的:

CL:在選定列地址后,就已經確定了具體的存儲單元,剩下的事情就是數據通過數據I/O通道(數據總線)輸出到內存總線上。但是在CAS發出之后,仍要經過一定的時間才能有數據輸出,從CAS與讀取命令發出到第一筆數據輸出的這段時間被稱為讀取潛伏期。tRP:在發出預充電命令之后,要經過一段時間才能允許發送行有效命令打開新的工作行,這個間隔被稱為預充電有效周期(Precharge command Period)。tRCD:在發送列讀寫命令時必須要與行有效命令有一個間隔,這個間隔被定義為tRCD,即RAS to CASDelay(RAS至CAS延遲),也可以理解為行選通周期。tRAS:行有效至預充電命令間隔周期。tRC:包括行單元開啟和行單元刷新在內的整個過程所需要的時間,所有參數可以從SDRAM數據手冊得到,計算出理論潛伏期時長為200/μs。

(4)其他設置

設置操作系統的入口點,這里用到的虛擬地址需要與系統中建立的映射表相對應。 #p#

3.2 BSP內代碼的實現

Windows CE系統啟動中,對SDRAM的操作分為兩個部分:首先對SDRAM的物理空間進行分配;其次將SDRAM所對應的物理地址轉換為虛擬地址。

3.2.1 地址的分配

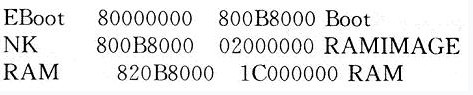

地址的分配和系統加載的順序有著密切的關系。首先要在內存中開辟一段空間用來存放啟動代碼BootLoader,它被存放在sDRAM的第一個區域空間內。當發生外部復位中斷時系統會從這里重新開始運行。其次分配操作系統內核空間,它被存放在SDRAM的第二個區域,以便使BootLoader能夠順利加載操作系統內核。分配地址空間根據所建立系統內核來確定。剩余的內存空間用來存放系統下的應用程序。

3.2.2 地址的映射

在操作系統中,需要把SDRAM的空間連續起來并作為首地址,不僅方便內存管理,而且當應用程序申請大塊內存時,操作系統內核也可方便的分配。這就引入了將不連續的物理地址空間映射為連續的虛擬地址空間。PXA255的SDRAM起始物理地址OxA0000000,可將其映射為0x80000000,這里0x80000000將作為系統虛擬空間的起始地址,當有IRQ中斷發生時,系統PC指針會重新指向這個地址。需要注意的是這里分配的虛擬地址要與啟動代碼中BootLoader中所使用的虛擬地址對應起來。

3.2.3 軟件的移植

針對于PXA27x系列的高端處理器,微軟在Plat-Build 5.0中給出了相對應的內核代碼雖然在內核代碼的架構上有了很大的變化,但對于擴展SDRAM的思想并沒有改變,首先在BootLoader中初始化所使用的SDRAM,其次在BSP內建立地址映射表。

4 結 語

文章主要介紹了在嵌入式Windows CE系統平臺上,使用大容量SDRAM作為動態存儲設備的方案。詳細介紹了SDRAM硬件連接方案以及軟件接口的實現。該方案已經在工程設計中投入使用,其可以在同類的嵌入式高端產品中推廣使用。

【編輯推薦】