AI做顯卡、顯卡跑AI!英偉達實現芯片設計自循環(huán)?

了解英偉達的研發(fā)情況,已經成為每年英偉達春季GTC會議的一個常規(guī)特征。

比如首席科學家兼研究部高級副總裁Bill Dally每年就會提供英偉達研發(fā)機構的概況和關于當前優(yōu)先事項的一些細節(jié)。

2022年,Dally主要關注英偉達正在開發(fā)和使用的AI工具,這些AI正在改善英偉達自身的產品。

如果愿意接受的話,這其實是一個巧妙的反向營銷案例:英偉達從制作顯卡來做跑AI工具的公司,成為了一家AI工具用來做顯卡的公司。

是的,英偉達已經開始使用AI智能來有效改善和加快自家的顯卡設計。

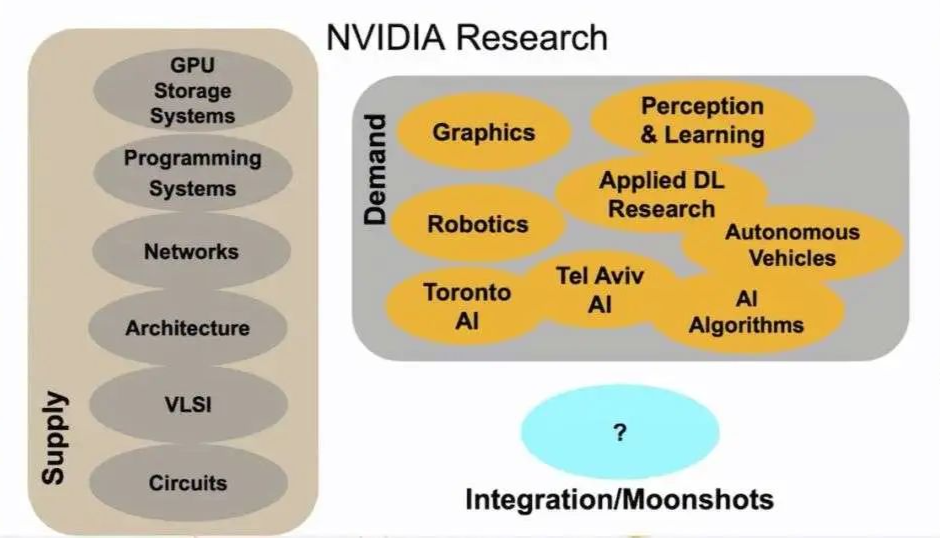

Dally在2022年的GTC演講中描述道:「我們的設計團隊是一個約有300人的小組,試圖在英偉達的產品設計上探索更有前瞻性的領先位置。我們有點像遠光燈,試圖照亮遠處的東西。這個團隊被松散地組織成兩半。

供應部分負責提供顯卡的技術。它使顯卡本身更好,從電路、到超大規(guī)模集成設計方法、架構網絡、編程系統(tǒng),以及讀入顯卡和基于顯卡的軟件的存儲系統(tǒng)。」

「需求部分試圖通過開發(fā)要用顯卡才能良好運行的軟件系統(tǒng)和技術,來推動市場對英偉達產品的需求。

例如我們有三個不同的圖形研究小組,因為我們在不斷推動計算機圖形技術的發(fā)展。我們還有五個不同的人工智能小組,因為使用GPU來運行AI是目前一個巨大的熱門,而且只會越來越熱。我們也有做機器人和自動駕駛汽車的小組。」

「我們還有一些以地域為導向的實驗室,如我們的多倫多和特拉維夫人工智能實驗室。」

偶爾,英偉達公司會從這幾個小組中抽出部分人力重組個登月式項目,例如,其中一次此類項目產生了英偉達的實時光線追蹤技術。

光追項目的組織架構圖

一如既往,2022年的研究與Dally上一年的談話有重復之處,但也有新的信息。比如該部門的規(guī)模肯定已經從2019年的175人左右增長了很多。毫無疑問,英偉達開發(fā)自動駕駛系統(tǒng)和機器人的努力也已經加強了。Dally沒有多說CPU的設計工作,這無疑也在增強。

接下來呈現的是Dally演講中關于英偉達在設計芯片時越來越多地使用AI的一小部分內容。

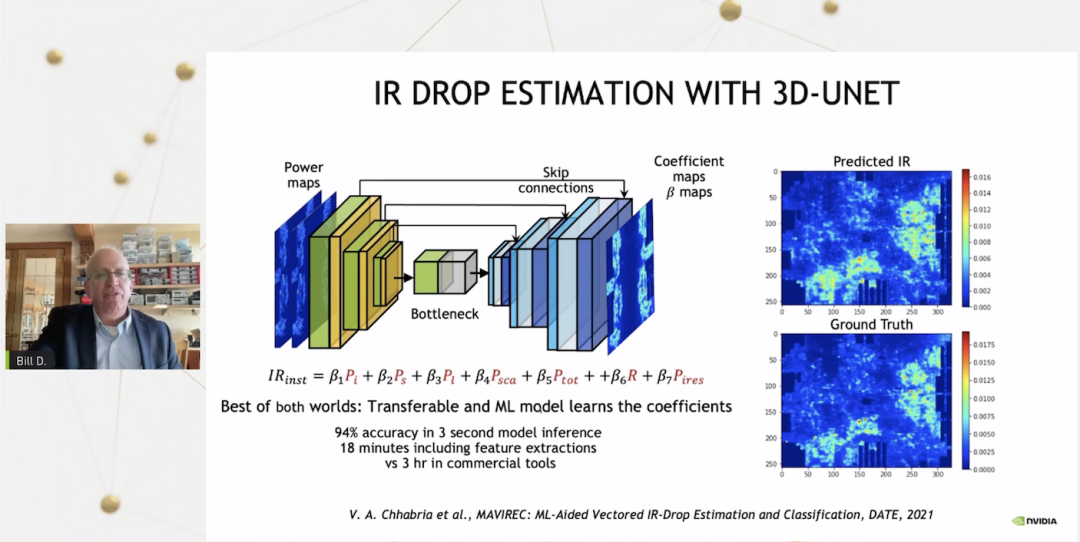

繪制電壓下降圖

Dally指出:「作為人工智能的專家,我們自然希望利用AI來設計更好的芯片。」

英偉達的顯卡設計部門以幾種不同的方式做到這一點。第一個也是最明顯的方法是,可以利用現有的計算機輔助設計工具,并將AI模型納入其中。

例如,顯卡設計部門有一個輔助設計的軟件工具,其中的AI實時測繪了英偉達的GPU顯卡產品中使用電力變化的位置圖譜,并實時預測電壓網格下降的程度。

一般電壓下降是用電流乘以電阻下降度算出,要在傳統(tǒng)的CAD工具上運算出這個值需要三個小時。因為這是一個迭代的過程,一直用傳統(tǒng)工具的話,對設計部門來說,工作量會變得非常艱巨。

概念展示

英偉達的顯卡設計部門想做的是訓練一個AI模型來獲取相同的數據。開發(fā)人員在一堆設計上如此試行過后,然后給AI輸入功率圖。AI由此產生的推理時間只有三秒。

當然,如果你包括上功率圖特征值提取的時間,那就是18分鐘。無論如何,與傳統(tǒng)效果相比這都是非常快的結果。

在類似的前提情況下,顯卡設計部門還嘗試了不使用卷積神經網絡AI、而是使用圖神經網絡的AI。如此處理的目的是為了估計顯卡電路中不同節(jié)點的開關頻率,這實際上推動了前述例子中的功率特征值輸入效率。

附帶的效果是,英偉達的開發(fā)人員能夠得到非常準確的顯卡電路功率估計,比傳統(tǒng)工具要快得多,而且只用了很小的一部分時間。

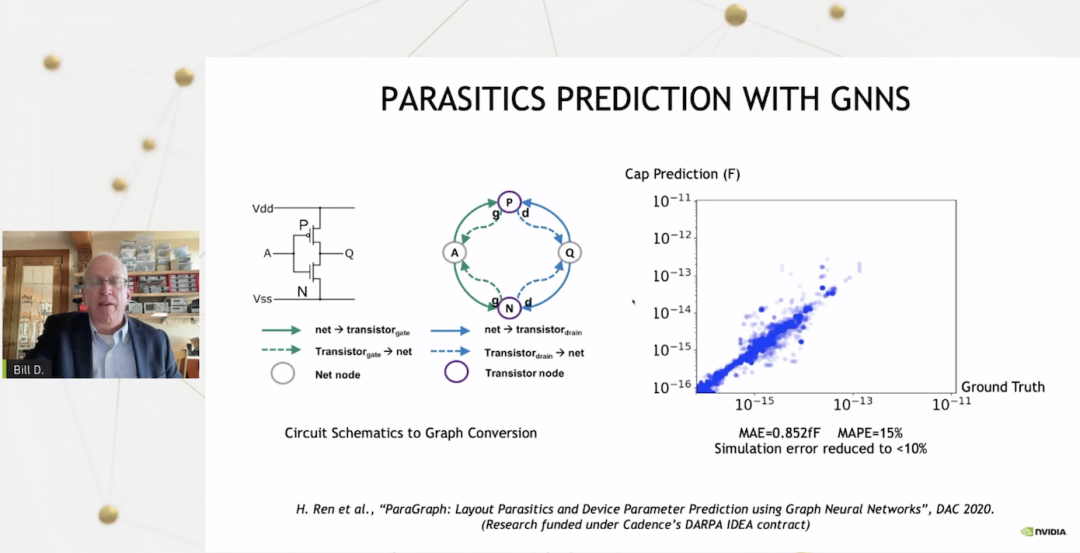

預測寄生元件

Dally特別喜歡的、若干年前他作為一名電路設計師投入相當多時間的設計項目,是用圖形神經網絡AI預測寄生元件(設計時未曾打算或預料到的電子元件)將會如何被附加到最終成品中。

過去,電路設計是一個非常反復的過程,設計師會畫出一個帶了一堆晶體管標志的電路原理圖。但他不會知道電路板的性能如何。

直到布局設計師拿著這個原理圖,做了布局樣品,附加了寄生元件,然后設計者才可以運行電路模擬,發(fā)現其中哪些部分不符合預期的設計規(guī)格。

然后設計師會返回去修改他的原理圖,并再次麻煩布局設計師再跑一遍這個流程,這是一個非常漫長的、反復的、不人性的勞動密集型過程。

現在英偉達的顯卡設計部門可以做到的,是訓練神經網絡來預測寄生元件,而不需要讓布局設計師制造布局樣品才發(fā)現瑕疵。

因此,電路設計者可以非常快速地迭代,而不需要在循環(huán)中重復進行手動設計-布局-再設計的步驟。

按Dally表示,與基礎真實值相比,現在英偉達的設計AI對這些寄生器件的預測非常準確。

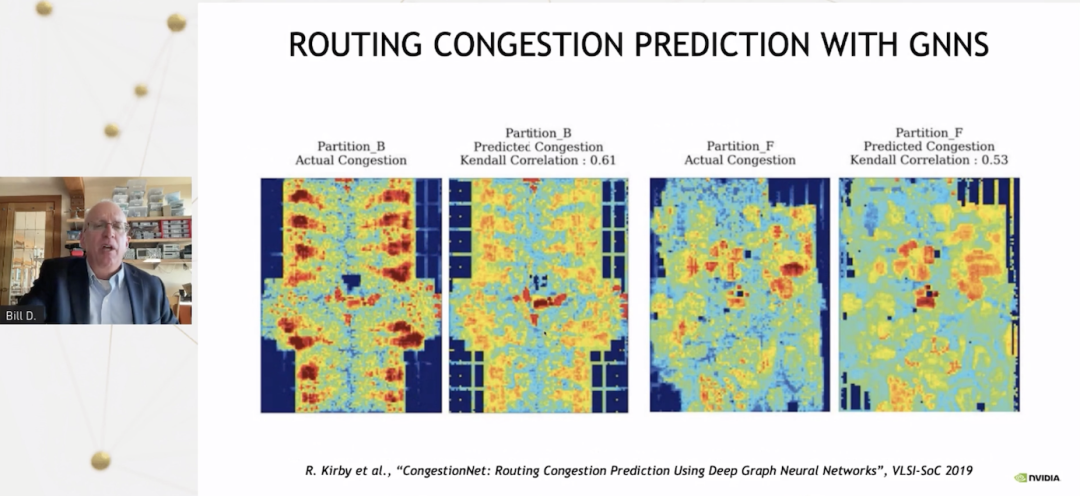

布局/布線擁塞

同時,我們還可以預測芯片的布局/布線帶來的擁塞問題,這對芯片的布局至關重要。

按正常的流程,芯片設計人員會做一張網格表,運行一遍布局和布線的過程。一般這個過程非常耗時,會花費數天的時間。

只有如此設計師們才能獲得顯卡樣品實際的擁塞情況,光有設計圖的初始布局是不夠的。

設計師們需要將其重構,并以不同的方式放置宏,以避開紅色的區(qū)域(如下圖所示)。紅色區(qū)域有太多交錯的線路穿過給定的區(qū)域,就像比特版「交通堵塞」。

而像這種情況,用上輔助設計的AI之后,沒必要再跑一邊布局和布線,就可以拿著這些網格列表,并用圖像神經網絡AI對擁塞出現的位置進行基本預測,結果還算準確。

雖說還不算完美,但是能顯示哪些區(qū)域存在問題。之后設計團隊就可以在特定區(qū)域采取行動,快速完成迭代,不再需要一遍遍重復全局布局和布線了。

芯片標準單元設計自動化

現有的方法都是用AI來評價人類的設計,而未來,更令人興奮的是能夠使用AI來完成設計。

Dally舉了兩個例子來說明AI如何完成芯片設計。

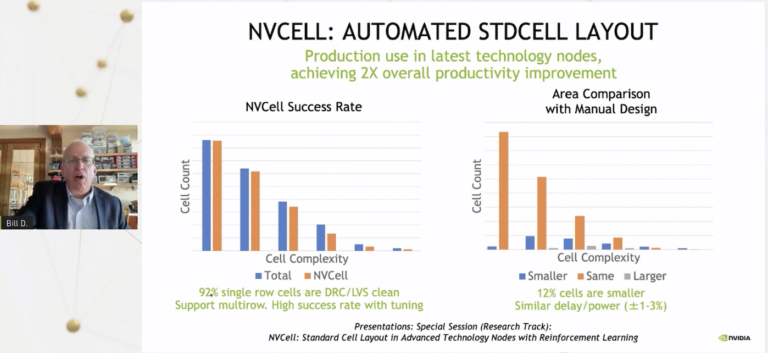

第一個系統(tǒng)叫NVCell,它結合了模擬低溫退火和加強學習,基本上能夠設計出數字集成電路的標準單元庫。

每次設計師實現了芯片技術上的升級——比方說從7納米優(yōu)化到5納米,設計師都會創(chuàng)造出一個單元庫。

一個單元就像是一個「與門」和「或門」,是一種完全的加速器。

眼下,英偉達的設計部門有數千個這種單元庫。這些單元需要在新技術的框架下,遵循一套復雜的設計標準,被重新設計。

第二個,是用強化學習模型來設計晶體管布局。

設計師們大部分都采用強化學習的辦法來放置晶體管。然而更重要的是,在晶體管放置后,一般都有很多設計規(guī)則上的錯誤,找到這些錯誤就像一款電子游戲一樣。

事實上,強化學習就擅長這個。一個很好的例子就是,強化學習在Atari電子游戲上的應用。

所以,這就像是一款Atari電子游戲,只不過,這次是一款修正標準單元中設計上存在的錯誤的游戲。

通過強化學習,英偉達的設計師可以篩查一遍出現的設計規(guī)則錯誤,然后修正它們。這樣,設計師就可以基本完成標準單元的設計工作了。

如下圖所示,92%的單元庫都可以用這個工具做好,不會存在任何設計規(guī)則上的錯誤或是電路上的錯誤。

此外,12%的單元比人工設計的單元都要小。總的來說,從單元的復雜性上看,AI設計的單元和人工設計的一樣好。

這可以幫助設計師完成兩件事。

第一,應用AI能極大地節(jié)省勞動力。沒有AI的話,大約需要一個10人小組耗時一年來建立一個新的技術庫。而如今,設計師可以用幾個GPU,跑幾天就行。

然后,人工只用介入剩下那8%AI未能完成的單元就好了。

在大多數情況下,設計師憑借AI往往能做出更好的設計。

所以說,不光省時省力,做出來的東西還更好。