GPT-4(o)免費試用體驗,看看它的設計方案能力—關于ROCE網卡方案

OpenAI 新發布了最新多模態AI 模型GPT-4o。這個模型的“4o”中的“o”代表“omni”,意為“全能的”。

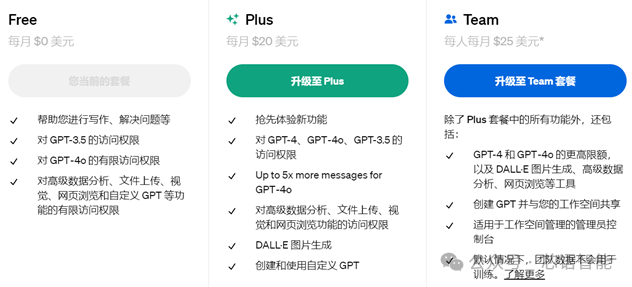

之前GPT-4的能力,聽說可以免費使用了,抓緊體驗一下世界頂級大模型。

原來免費套餐也是有對GPT-4o有限訪問權限。

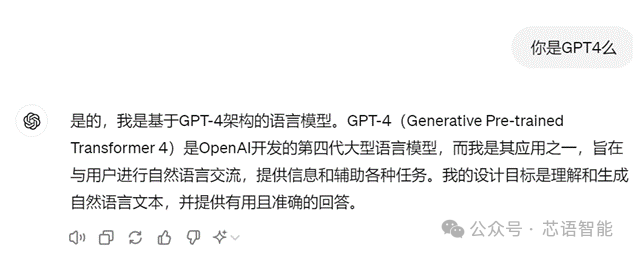

問一下,確認一下模型身份。

機會難得,找個難一點的問題來問。數據中心、高性能計算、人工智能、機器學習和存儲等應用 需要高性能網卡,問下怎么設計高性能網卡。

問題1:想設計高性能網卡,請給出模塊化設計方案:設計基于RoCEv2協議的高性能網卡,比如采用FPGA進行硬件加速,通過軟硬件結合,考慮滿足性能和提高開發進度,模塊化設計分為如下幾個模塊,功能盡量解耦,方便并行開發。

答:設計一個基于FPGA進行硬件加速的RoCEv2 RDMA高性能網卡,可以通過模塊化設計來實現,軟硬件結合,提高性能和開發進度。以下是一個可能的模塊化設計方案,每個模塊的功能盡量解耦,以便于并行開發。

1. **傳輸層協議引擎**

- 功能:處理RoCEv2協議的UDP/IP封裝和解封裝,錯誤處理和流量控制。

- 建議:該模塊相當重要,建議詳細設計內部子模塊,例如:

- **封裝/解封裝子模塊**:專門處理UDP/IP封裝和解封裝。

- **流量控制子模塊**:處理RoCEv2的流量控制機制,如擁塞控制。

- **錯誤處理子模塊**:處理網絡傳輸中的各種錯誤。

2. **隊列對管理器**

- 功能:管理RDMA操作中的隊列對,如發送隊列(SQ)、接收隊列(RQ)和完成隊列(CQ)。

- 建議:可以進一步細化管理機制,例如:

- **隊列調度子模塊**:優化SQ、RQ、CQ的調度策略。

- **隊列狀態監控子模塊**:實時監控隊列狀態,優化性能。

3. **內存管理單元**

- 功能:處理內存地址轉換、訪問權限驗證和內存保護。

- 建議:此模塊可以劃分為以下子模塊:

- **地址轉換子模塊**:負責虛擬地址到物理地址的轉換。

- **權限驗證子模塊**:確保訪問權限的正確性。

- **內存保護子模塊**:防止非法內存訪問,提供數據保護。

4. **網絡接口和物理層**

- 功能:實現與物理以太網的連接,處理MAC和PHY層的功能。

- 建議:可以細分為:

- **MAC層處理子模塊**:負責以太網幀的發送和接收。

- **PHY層處理子模塊**:處理物理層的電氣信號轉換和連接。

5. **完整性和性能監控**

- 功能:監控網絡和設備的性能,確保數據傳輸的完整性和正確性。

- 建議:此模塊可以進一步細化為:

- **性能監控子模塊**:實時監控網絡性能,提供統計和分析。

- **完整性檢測子模塊**:確保數據在傳輸中的完整性。

6. **管理配置**

- 功能:提供網卡的配置和管理功能,包括固件升級、參數設置等。

- 建議:可以增加一些具體的功能模塊:

- **固件管理子模塊**:處理固件升級和版本管理。

- **配置管理子模塊**:處理各種參數設置和保存。

7. **安全模塊**

- 功能:提供數據加密和完整性檢驗,確保安全通信。

- 建議:細分為:

- **數據加密子模塊**:處理數據的加密和解密。

- **完整性檢驗子模塊**:驗證數據的完整性,防止篡改。

8. **日志與調試模塊**

- 功能:提供系統日志記錄和調試功能,便于開發和維護。

- 建議:包括日志記錄子模塊和調試接口子模塊。

9. **兼容性和擴展模塊**

- 功能:確保網卡與其他系統的兼容性,并支持未來擴展。

- 建議:包括協議兼容子模塊和擴展接口子模塊。

通過這些細化和擴展,整個設計將更具模塊化和系統性,方便并行開發和未來的維護與升級。回答的還挺專業啊,像模像樣。網卡方案分為幾個模塊,傳輸層協議引擎:處理RoCEv2協議的UDP/IP封裝和解封裝,錯誤處理和流量控制。隊列對管理器:管理RDMA操作中的隊列對,如發送隊列(SQ)、接收隊列(RQ)和完成隊列(CQ)。內存管理單元:處理內存地址轉換、訪問權限驗證和內存保護。網絡接口和物理層:實現與物理以太網的連接,處理MAC和PHY層的功能。完整性和性能監控:監控網絡和設備的性能,確保數據傳輸的完整性和正確性。管理配置:提供網卡的配置和管理功能,包括固件升級、參數設置等。安全模塊:提供數據加密和完整性檢驗,確保安全通信。 再問的細致點試試? 問題2 軟硬件結合分工,需要考慮開發進度要求,在滿足性能和靈活性的條件下,軟件和硬件功能方面怎么分配更優化呢? 答:在設計基于FPGA的硬件加速解決方案時,需要在性能和開發進度之間找到一個平衡點。軟硬件結合的設計應當充分利用FPGA的并行處理能力,同時保持靈活性,便于軟件層的更新和維護。以下是優化軟硬件分配的一些建議:

1. 傳輸層協議引擎

- 硬件實現:

封裝/解封裝子模塊:利用FPGA并行處理能力加速UDP/IP封裝和解封裝。

流量控制子模塊:硬件實現擁塞控制以提高實時性和效率。

錯誤處理子模塊:基本的錯誤檢測和糾錯可以硬件實現,提供低延遲的錯誤處理。

- 軟件實現:

高級流量管理策略可以通過軟件實現,便于調整和優化。

復雜的錯誤處理和恢復邏輯可以在軟件中處理,以便于維護和更新。

2. 隊列對管理器

- 硬件實現:

隊列調度子模塊:硬件實現基本的隊列調度,確保低延遲。

隊列狀態監控子模塊:硬件實時監控隊列狀態,提高響應速度。

- 軟件實現:

高級調度策略和隊列優化算法可以由軟件實現,以提高靈活性。

非關鍵路徑的狀態監控和統計分析可以由軟件處理。

3. 內存管理單元

- 硬件實現:

地址轉換子模塊:硬件實現虛擬到物理地址轉換,確保高效。

權限驗證子模塊:硬件實現基本的訪問權限驗證,提高安全性和效率。

- 軟件實現:

復雜的權限管理策略和動態調整可以通過軟件實現,以增強靈活性。

內存保護策略可以由軟件動態配置和調整。

4. 網絡接口和物理層

- 硬件實現:

MAC層處理子模塊:硬件實現以太網幀處理,確保低延遲和高吞吐量。

PHY層處理子模塊:硬件處理物理層信號轉換,確保穩定的物理連接。

- 軟件實現:

- 配置和管理PHY層參數可以通過軟件實現,以便于調試和維護。

5. 完整性和性能監控

- 硬件實現:

性能監控子模塊:硬件實現實時性能監控,提供高精度的數據。

完整性檢測子模塊:硬件實現基本的數據完整性檢查,提高實時性。

- 軟件實現:

- 復雜的性能分析和數據處理由軟件實現,便于靈活調整和優化。

- 長期統計和報告生成由軟件處理。

6. 管理配置

- 軟件實現:

固件管理子模塊:軟件實現固件升級和版本管理,提高靈活性。

配置管理子模塊:軟件實現各種參數設置和保存,便于更新和維護。

7. 安全模塊

- 硬件實現:

數據加密子模塊:硬件實現數據加密和解密,提供高性能的安全處理。

完整性檢驗子模塊:硬件實現基本的完整性檢驗,提高實時性和效率。

- 軟件實現:

復雜的加密策略和安全協議由軟件實現,便于靈活調整和更新。

高級安全管理和策略配置由軟件處理。

8. 日志與調試模塊

- 軟件實現:

日志記錄子模塊:軟件實現系統日志記錄,便于調試和維護。

調試接口子模塊:軟件實現調試接口,提供靈活的調試手段。

9. 兼容性和擴展模塊

- 軟件實現:

協議兼容子模塊:軟件實現各種協議兼容,便于靈活更新和維護。

擴展接口子模塊:軟件實現擴展接口,便于未來的功能擴展和升級。 通過以上分配,硬件模塊主要承擔實時性和高性能要求較高的功能,軟件模塊則負責復雜的邏輯處理和靈活的策略管理。這種分配可以確保開發進度的同時,充分利用FPGA的硬件加速能力,提高整體系統的性能和靈活性。

再問的細致一點,看看模塊之間咋搞。

問題3:傳輸層協議引擎和網絡接口及物理層之間的對接接口設計分析?答3 :傳輸層協議引擎和網絡接口及物理層之間的對接接口,我們需要考慮它們之間的數據流、控制信號和狀態信號的交互。以下是詳細分析:

數據信號

- 傳輸數據信號(Tx Data)

從傳輸層協議引擎到網絡接口的傳輸數據。

通常為數據包的實際內容(例如以太網幀)。

- 接收數據信號(Rx Data)

從網絡接口到傳輸層協議引擎的接收數據。

包括接收到的數據包(例如UDP/IP數據)。

控制信號

- 傳輸數據有效信號(Tx Data Valid)

傳輸層協議引擎通知網絡接口有有效數據需要傳輸。

- 接收數據有效信號(Rx Data Valid)

網絡接口通知傳輸層協議引擎接收到有效數據。

- 傳輸數據準備好信號(Tx Data Ready)

網絡接口通知傳輸層協議引擎可以發送數據。

- 接收數據準備好信號(Rx Data Ready)

傳輸層協議引擎通知網絡接口可以接收數據。

- 流量控制信號(Flow Control)

雙方協調傳輸速率,防止數據丟失或緩沖區溢出。

狀態信號

- 傳輸狀態信號(Tx Status)

網絡接口反饋傳輸狀態,如傳輸成功、傳輸失敗等。

- 接收狀態信號(Rx Status)

傳輸層協議引擎反饋接收狀態,如接收成功、校驗錯誤等。

- 鏈路狀態信號(Link Status)

網絡接口反饋物理鏈路狀態,如鏈路連接、鏈路斷開等。

接口信號詳細描述

- ?數據信號

Tx_Data[WIDTH-1:0]:寬度根據實際數據寬度確定(如32位、64位等)。

Rx_Data[WIDTH-1:0]:同上,接收數據寬度。

- 控制信號

Tx_Data_Valid: 表示傳輸數據有效。

Rx_Data_Valid: 表示接收數據有效。

Tx_Data_Ready: 表示可以發送數據。

Rx_Data_Ready: 表示可以接收數據。

Flow_Control?: 表示流量控制狀態,如pause信號。

- 狀態信號

Tx_Status[STATUS_WIDTH-1:0]: 傳輸狀態信號,包含成功、失敗、重試等信息。

Rx_Status[STATUS_WIDTH-1:0]: 接收狀態信號,包含成功、錯誤、重試等信息。

Link_Status?: 物理鏈路狀態,如0?表示斷開,1表示連接。

接口信號示例

```verilog

// 數據信號

wire [31:0] Tx_Data;

wire [31:0] Rx_Data;

// 控制信號

wire Tx_Data_Valid;

wire Rx_Data_Valid;

wire Tx_Data_Ready;

wire Rx_Data_Ready;

wire Flow_Control;

// 狀態信號

wire [7:0] Tx_Status;

wire [7:0] Rx_Status;

wire Link_Status;

```總結

通過上述分析,可以形成如下對接接口的設計方案:

- ?數據信號(Tx_Data, Rx_Data):用于傳輸和接收數據。

- 控制信號(Tx_Data_Valid, Rx_Data_Valid, Tx_Data_Ready, Rx_Data_Ready, Flow_Control):用于控制數據傳輸和接收的有效性和準備狀態。

- 狀態信號(Tx_Status, Rx_Status, Link_Status):用于反饋傳輸、接收和鏈路狀態。 這些信號可以通過標準的接口(如AXI4-Stream、Avalon-ST等)來實現,以確保傳輸層協議引擎與網絡接口及物理層之間的高效、可靠通信。這些信號的定義和具體實現可以根據FPGA平臺和實際需求進行調整和優化。