芯片設計大佬放狠話:未來10年,芯片性能提高1000倍

AI設計的芯片性能十年內將提高1000倍。

作為Synopsys首席執行官、芯片設計自動化的先驅之一,Aart de Geus在Hot Chips在線芯片大會上表示,現在人工智能設計的芯片,性能可能會在未來十年內提高1000倍。

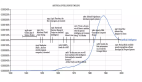

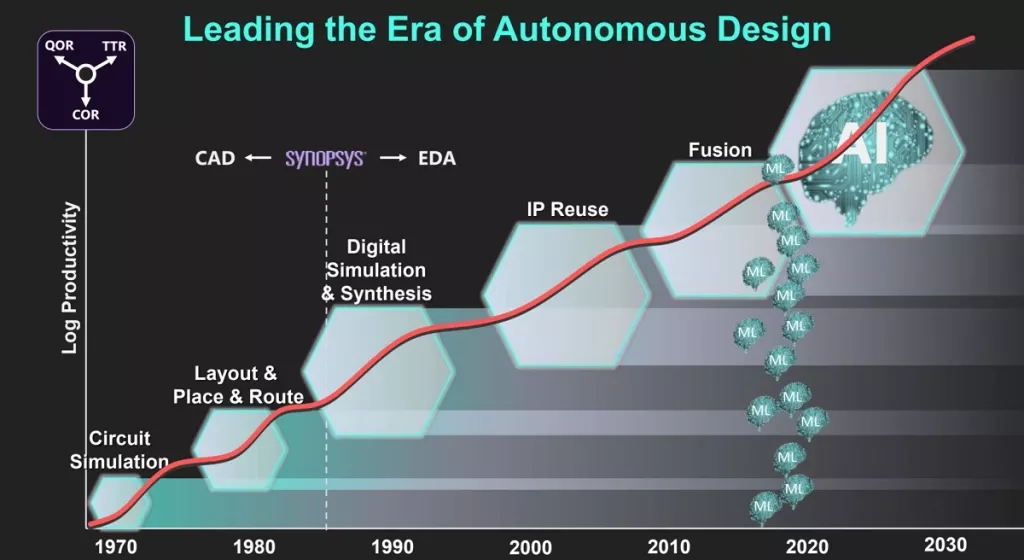

自80年代以來,自動化一直都是芯片設計的一部分。

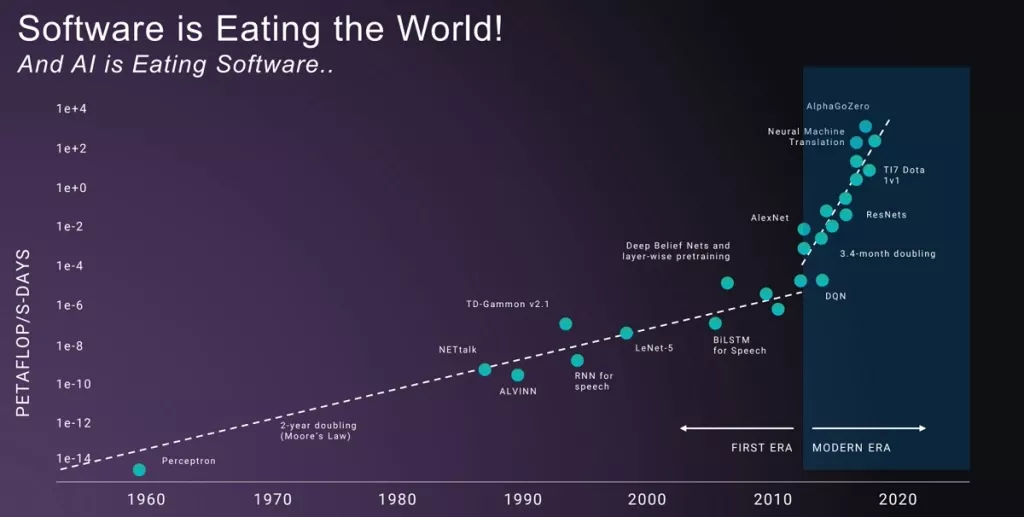

但現在,每兩年芯片性能翻一番的「摩爾定律」似乎已經達到了瓶頸。

要突破這個瓶頸,最好的辦法或許就是你我都熟知的:

人工智能。

https://www.nature.com/articles/d41586-021-01515-9

一篇刊登在Nature上的文章指出,經過訓練的機器學習系統在芯片設計上的表現超過人類。

不少芯片架構師都擔心自己的飯碗未來會被AI搶走。

不過De Geus卻認為,芯片架構師不僅不會下崗,還會轉移到產業鏈的上游,比現在負責更多任務。

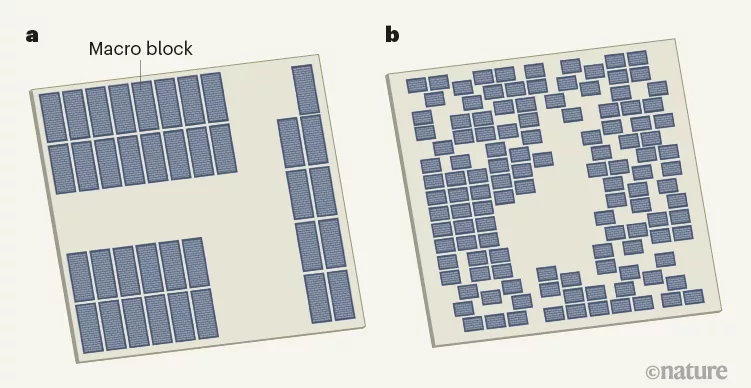

人類設計的芯片平面圖(a)與機器學習系統生成的平面圖(b)

Synopsys從去年開始就使用AI來設計客戶的芯片,與人工設計的芯片相比有了相當大的改進。

目前,三星也正在使用Synopsys的工具DSO.ai來設計Exynos芯片。

而它的競爭對手Cadence Design Systems也在今年推出了自己的人工智能芯片設計項目。

打破摩爾定律瓶頸

De Geus在1986年創立了Synopsys,一家電子設計自動化(EDA)軟件公司。

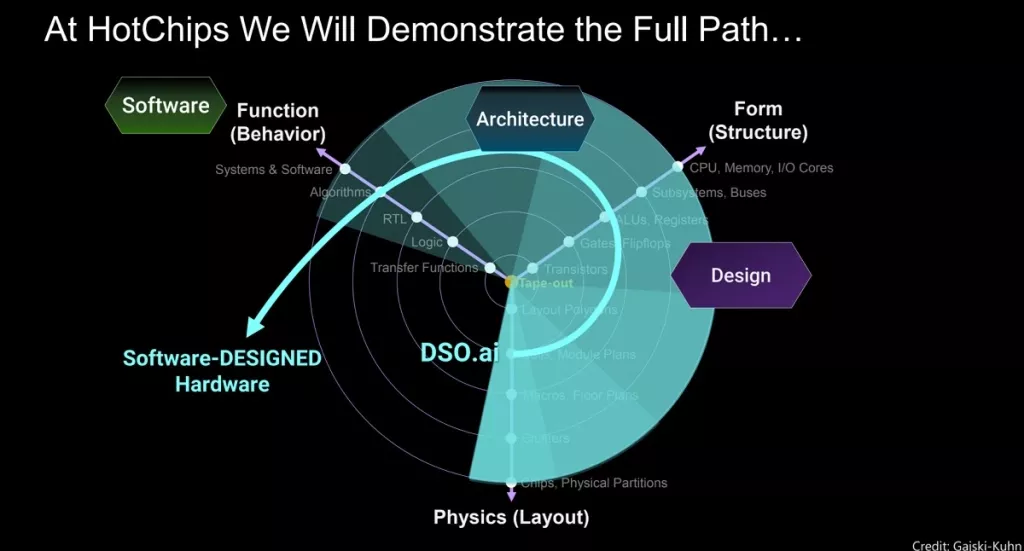

憑借多年尖端半導體設計經驗,Synopsys利用這個寶貴的資產制作了第一代AI芯片軟件DSO.ai。

要想超越摩爾定律,就要利用AI來解決復雜性、功耗和擴展要求,最終實現1000倍性能的目標。

「機器學習出現在我們使用的每一種工具中,這個設計空間優化(DSO)的新工具的不同之處在于,它不適用于單個設計步驟,而是適用于整個設計流程。」

這就是Synopsys采用的自主芯片設計方法,從綜合方法進行芯片設計,而不僅僅是芯片布局。

摩爾定律逐漸扁平,芯片設計重任落到了AI肩上

芯片設計的一個早期步驟是floor planning,其確定了芯片的尺寸、標準單元的排列形式、IO單元及宏單元的位置、電源地網絡的分布等。

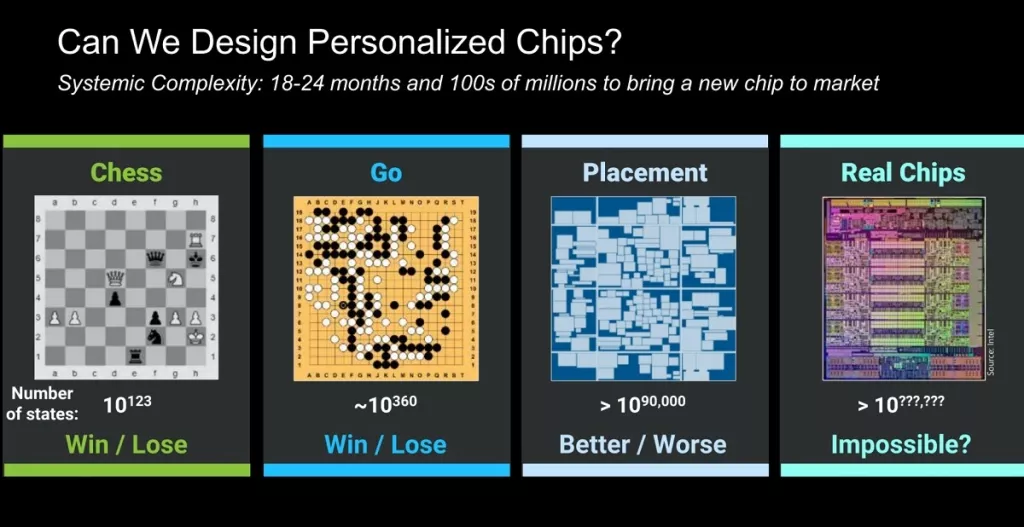

由于宏單元潛在配置數量巨大(約為10^2500),規劃就會變得非常復雜,而且隨著邏輯電路設計的發展,還需要進行多次迭代。

如果每次迭代都由人類工程師手動生成,就要耗時數天或數周。

在芯片設計的新時代,自動化大不相同

但如果用AI設計芯片,它就能夠利用強化學習,優化芯片的功率、性能和面積大小。

還能解決針對特定應用程序以及系統的所有維度的快速定制芯片:硬件(物理)、軟件(功能)、可制造性和架構(形式)。

隨著AI接管更多任務,以往負責設計少量晶體管的工程師,現在可能負責設計更大芯片中的10億個晶體管。

這樣就能夠在更短的時間內設計出更快的芯片,改變芯片的架構,將芯片性能提高10倍、100倍甚至是1000倍。

歡迎來到AI芯片設計時代

與使用最先進設計工具的世界一流設計團隊相比,DSO.ai能夠將功耗降低25%,性能是當下最好的AI芯片設計工具的5倍。

而在未來的AI芯片設計時代,芯片能夠根據各個垂直行業進行設計。

芯片定制會更普遍

面對特定項目的差異化需求,DSO.ai可以用來優化輸入參數以及芯片設計工作流程的選擇。

工程師可以使用DSO.ai進行更多設計流程中的參數輸入,例如微調庫單元以提供最佳頻率或最低功率,采用現有平面圖并盡量縮小芯片尺寸,確定多高的工作電壓會實現功耗與性能的最佳權衡等。

全球「缺芯」,雖然說不少行業都受到影響,但人們也深刻認識到了芯片的重要性。

芯片雖小,但卻是一個重要的基礎設施。

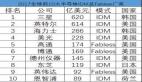

除了Synopsys,谷歌、英偉達也開始嘗試使用人工智能技術設計芯片。

谷歌的TPU(張量處理單元)芯片即將發布新版本,優化了人工智能計算。

目前英偉達也專注于使用AI技術生產更好的GPU和云計算TPU平臺,以增強自身競爭力。

芯片設計的工程師不會下崗。

而人工及AI相結合的設計思路將會推動芯片設計邁進人工智能時代。